|

Технология ПЛИС и ее применение для создания нейрочипов

Приборы программируемой логики уже давно применяются для построения интерфейсных узлов, устройств управления и контроля и т. д., однако до недавнего времени они занимали достаточно скромное положение. Сегодня ситуация меняется. |

Программируемые логические матрицы (Field-Programmable Gate Array, FPGA) появились в 1985 году по инициативе компании Xilinx, предложившей «микросхему-конструктор» – полупроводниковый кристалл с цифровыми компонентами без жестко зафиксированных металлических соединений, формирующих конкретную схему. Соединениями в FPGA можно управлять путем замыкания транзисторных ключей, во множестве размещенных на том же кристалле. На протяжении десятилетий характеристики FPGA (или ПЛИС) постоянно улучшались, объем выпуска увеличивался, а спектр применений расширялся, в частности для суперкомпьютеров. Чем привлекательны эти реконфигурируемые платформы и какова их сфера применения?

Начинка FPGA

Базовый элемент FPGA – логическая ячейка (рис. 1), содержащая логический генератор и триггеры. Логический генератор – «визитная карточка» FPGA – блок статической памяти, заполненной таблицей выходных значений. Для шести входов возможны 64 комбинации входных сигналов, таким образом, для реализации логического генератора требуется 64 бит памяти. Получается, что внутри FPGA расположены не базовые логические элементы И, ИЛИ, НЕ и т. п., а таблицы значений, с помощью которых можно имитировать любую комбинацию этих элементов. Выходы логических генераторов могут быть записаны в триггер, а могут быть и пущены в обход его, что позволяет при наличии достаточного количества логических ячеек-«кубиков» построить цифровую схему практически любой сложности.

.png) |

| Рис. 1. Логическая ячейка FPGA |

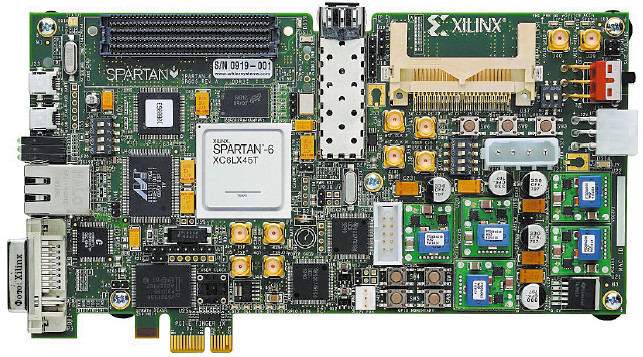

Сегодня микросхемы с архитектурой FPGA выпускают Altera, Actel, Lattice, Xilinx и ряд других компаний. Наибольший интерес представляет продукция Xilinx и Altera, выпускающих в целом паритетную продукцию. Кристаллы FPGA двух основных серий, выпускаются с применением технологических норм 40/45 нм. В дешевом семействе Spartan-6 количество матриц логических ячеек достигает 150 тыс., а в Virtex-6 может быть до 750 тыс. таких ячеек. Однако не только логические ячейки определяют привлекательность FPGA для разработчиков.

|

HPC – конец мелового периода

В живой природе у каждого вида есть свой предел роста, предопределенный генетическим кодом. В технике такого барьера нет, а потому иногда инженеры нарушают пределы разумного, и тогда на свет появляются монстры. |

По сравнению с обычными микросхемами FPGA обладают двумя существенными недостатками: они дороже и работают на меньшей тактовой частоте. Это связано с тем, что их ячейки содержат больше элементов, чем схожие по назначению компоненты специализированных микросхем, поэтому реализация схемы из программируемых «кубиков» потребует большей площади, чем аналогичная схема, созданная для решения строго одной задачи. Кроме того, связи между компонентами FPGA содержат своеобразные «стыки» в виде программируемых точек соединения, из-за чего частота работы оказывается меньше, чем для специализированной микросхемы, выполняемой по такому же технологическому процессу. В итоге получается медленный и дорогой испытательный стенд для проектирования новых микросхем.

В 90-х годах компания Xilinx заняла часть рынка, традиционно связываемую с сигнальными процессорами (DSP), что было на первый взгляд несколько неожиданно – сигнальный процессор является специализированной микросхемой, так что его можно считать оптимальным решением для цифровой обработки сигналов. Однако сигнальные процессоры обычно имеют один-два блока для собственно цифровой обработки, а остальная часть кристалла содержит ядро процессора, память, периферийные устройства и т. п. Ориентация на массовый выпуск микросхем приводит к тому, что их производители стараются разместить на кристалле набор устройств, охватывающих решения для существенной доли рынка, а для задач с небольшим тиражом приходится подбирать максимально близкую по параметрам, но все же не идеально подходящую микросхему. Поэтому в каких-то случаях оказывается возможным заполнить FPGA набором однотипных устройств, которые в сумме обеспечат большую производительность, чем процессор. Например, запрограммировав FPGA на выполнение операций «умножение с накоплением», можно получить производительность существенно выше, чем у сигнальных процессоров. Причем лучше оказывается не только сама производительность, но и соотношение производительность/цена, несмотря на то что ресурсы ячеек используются далеко не полностью, а рабочая частота невысока.

|

Программная настраиваемость аппаратной структуры

Для построения современных высокопроизводительных систем необходимо применение реконфигурируемых структур, настраиваемых на исполнение алгоритмов. |

В последующих после первых чипов FPGA XC4000 поколениях компания Xilinx добавляет на кристалл специализированные умножители, эволюционировавшие в дальнейшем в блоки цифровой обработки сигналов, способные выполнять умножение с накоплением на высокой тактовой частоте. Такие блоки не имеют недостатков, присущих программируемым ресурсам FPGA, поскольку представляют собой фрагмент кристалла, выполняющий строго определенную, фиксированную задачу. По техническому исполнению они представляют собой так называемые hard-IP, непрограммируемые компоненты, размещаемые в FPGA потому, что выполняемая ими функция широко востребована, а реализация в программируемых ячейках не слишком эффективна. Иными словами, широко распространенную операцию умножения с накоплением в FPGA выполняют точно такие же модули, что и в сигнальных процессорах. Однако разница заключается в том, что таких блоков намного больше (рекордные по объему FPGA имеют их несколько тысяч), и программируемые ячейки могут служить своеобразным «клеем», реализуя операции, которые в сигнальных процессорах отданы прикладной программе. С помощью аппаратных блоков цифровой обработки сигналов FPGA могут выполнять целый ряд вычислительных задач с высокими требованиями к производительности: цифровую фильтрацию, спектральный и вейвлет-анализ (анализ различных частотных компонентов данных), аппаратную реализацию нейросетей и т. п.

Блоки цифровой обработки сигналов – не единственный аппаратный компонент в FPGA, на рис. 2 можно также увидеть блочную память и приемопередатчики. Первый из компонентов часто выступает как органичное дополнение блоков цифровой обработки сигналов, поскольку для многих алгоритмов требуется хранение обрабатываемых данных или дополнительных коэффициентов. Это обычная статическая память, аналогичная кэш-памяти процессоров. По аналогии с блоками цифровой обработки, появление такой памяти связано с тем, что реализовать ее с помощью программируемых ячеек возможно, но очень накладно – характеристики такого блока будут далеки от оптимальных, а расход программируемых ресурсов чрезвычайно высок. Объем блоков памяти, однако, не так велик и составляет до 85 Мбит (хотя в FPGA приемлемой стоимости можно ожидать скорее сотен килобитов). Это означает, что в задачах, требующих больших объемов памяти, FPGA не могут предложить каких-либо выгод. Вообще говоря, с помощью программируемых ячеек можно подключить к кристаллу и внешнюю память DDR2 или DDR3, но в этом случае количество подключаемых модулей ограничено числом внешних выводов FPGA.

Компоненты другого типа также призваны выполнять функцию, чрезвычайно неудобную для реализации в программируемых ячейках – это скоростные последовательные приемопередатчики, способные передавать данные со скоростями до десятков гигабитов в секунду. С их помощью можно реализовать такие интерфейсы, как SATA, Gigabit Ethernet, HyperTransport, PCI Express, Infiniband и др. Особенностью таких модулей является практически полная невозможность представить их в виде только цифровых компонентов, поскольку для обеспечения высоких частот передачи требуются и аналоговые компоненты.

Что же могут FPGA в качестве компонента вычислительной платформы? На рис. 2 схематично показано соотношение производительности основных компонентов FPGA. Если рассматривать микросхемы предельного на сегодня объема (2 млн логических ячеек для Virtex-7), то в такое устройство можно ввести поток данных с суммарной пропускной способностью порядка 500-1000 Гбит/с, что зависит от числа выводов, которые будут для этого использованы (предельная частота обмена по обычным линиям ввода-вывода на сегодня составляет 1,4 Гбит/с). Массив блоков цифровой обработки способен на пике производительности обеспечить более 5 TMAC/с (Terra Multiply and Accumulate, умножение с накоплением на целочисленных операндах), и с учетом разрядности умножителей и аккумуляторов на кристалле каждую секунду образуется до 30 Тбайт. Приемопередатчики способны «отвести» до 2 Тбит/с, и в итоге внутри кристалла оказывается примерно в 100 раз больше данных, чем их можно доставить или забрать. Положение не слишком спасает и память – на кристалле ее немного, а возможности подключения внешней памяти ограничены числом выводов корпуса (можно отметить, правда, что двух- и четырехканальная память для FPGA не представляет особой проблемы – контроллеры памяти выполняются в желаемом количестве путем программирования части ячеек).

.png) |

| Рис. 2. Соотношение производительности основных компонентов FPGA |

Что считать в FPGA?

Для каких же задач можно эффективно использовать FPGA, с учетом ее высокой стоимости и сложности разработки? Формально, можно добиться очень высокой производительности вычислений, однако внешние интерфейсы не обеспечивают такого же высокого прироста производительности, как внутренние ресурсы, поэтому на первый план выходит высокая цена FPGA, которая и вынуждает отказаться от этих микросхем в пользу процессорных решений. Действительно, миллиарды и триллионы операций на кристалле – очень высокий показатель, но FPGA не способны обеспечить сквозной поток данных такого объема. Схожие проблемы возникают с рядом суперкомпьютерных задач – например, с помощью FPGA нерационально обрабатывать массивы внешней памяти в десятки и сотни гигабайтов. Такого объема памяти на кристалле нет, а возможности подключения внешних микросхем памяти ограничены количеством внешних выводов FPGA. Таким образом, хотя FPGA и может обрабатывать больше данных, чем современные процессоры, этот прирост не всегда оказывается таким существенным, чтобы оправдать более высокую цену и сложность проектирования.

Итак, понятно, что задача наподобие моделирования трехмерных объектов с размером модели в десятки гигабайтов не вполне подходит для FPGA. Равномерную нагрузку на кристалл можно получить, когда относительно небольшой объем входных данных подвергается интенсивной обработке. Примером могут служить цифровые фильтры высоких порядков – на каждый входной отсчет требуется количество операций, пропорциональное порядку фильтра. Другими примерами эффективного использования ресурсов FPGA являются быстрое преобразование Фурье и вейвлет-преобразование, для которых характерно большое число операций над небольшим объемом входных данных. Обработка изображений, анализ сетевого трафика, криптография также относятся к задачам, удобным для реализации в FPGA.

FPGA для пользователя

Стоит ли рядовому потребителю ожидать появления некоей платы с FPGA, которая может быть установлена в его домашний компьютер, в результате чего сам потребитель увидит улучшение каких-либо его характеристик? Сравнивая FPGA с графическими ускорителями, можно заметить определенное сходство – в компьютер устанавливается дополнительное оборудование, выполняющее часть функций, ранее выполнявшихся центральным процессором. Отличие в том, что графические ускорители решают задачу, ценность которой вполне понятна – потребители готовы платить за качественное изображение. Современные модели к тому же ускоряют не только графику и видео высокого разрешения, но и параллельные вычисления (например, с помощью библиотеки OpenCL). Правда, эффективно ускоряемые алгоритмы достаточно специфичны – вычислительные ресурсы графического ускорителя оптимизированы для выполнения конкретных операций, характерных для графики.

Библиотека OpenCL – относительно свежий инструмент, который еще не успел стать привычным для широкого круга программистов, причем речь идет об использовании вполне определенной аппаратной архитектуры. Реконфигурируемая платформа, которой являются FPGA, очертит значительно более широкий круг задач, ведь, перед тем как программировать ускоритель, его надо будет создать из конфигурируемых ресурсов FPGA. Это существенное препятствие для программиста, который рассчитывает на автоматическую поддержку аппаратуры драйверами от производителя. Однако для разработчиков, планирующих предложить пользователям комбинированное аппаратно-программное решение, FPGA представляет собой эффективный вариант по сравнению со специализированными микросхемами.

.png) |

| Рис. 3. Мультипроцессорная система на базе FPGA |

Для решения вычислительных задач сегодня применяются различные процессорные архитектуры в сочетании с непрограммируемыми аппаратными узлами: SISD (Single Instruction, Single Data), которые используются как процессоры общего назначения; SIMD (Single Instruction, Multiple Data), предназначенные для операций с векторами данных (например, мультимедийной обработки); MIMD (Multiple Instruction, Multiple Data) – матрицы процессорных элементов. На рис. 3 представлена комбинированная система, содержащая процессоры с различными архитектурами. Такой подход (many core) рассматривается как альтернатива multicore, подразумевающему использование однотипных процессорных ядер. С помощью такой гетерогенной вычислительной среды можно оптимально распределить нагрузку между ядрами. Реконфигурируемость аппаратуры – несомненный плюс, ведь появляется возможность реализовать в каждом процессоре именно те возможности, которые потребуются ему для решения определенного класса задач. Такое свойство недостижимо ни для процессоров общего назначения, ни для графических ускорителей, поскольку они должны содержать все устройства, которые когда-либо могут быть востребованы программистом. Нетрудно представить, как мала эффективность процессора с архитектурой x86, выполняющего операцию суммирования многогигабайтного массива или сравнения двух массивов. Аппаратные затраты на такую операцию в FPGA несопоставимо малы, а узкая применимость задачи неважна, ведь для другой задачи может быть загружена другая конфигурация.

Перспективы

Современными продуктами Xilinx можно считать FPGA 6-й серии: Virtex-6 и Spartan-6. Анонсированы FPGA 7-й серии, запланированные к выпуску в 2012 году, которые будут производиться с соблюдением норм 28 нм и состоять из трех семейств: Virtex-7 традиционно для Xilinx представляют собой микросхемы максимально возможного объема, содержащие полный набор дополнительных компонентов, в частности планируются кристаллы с 3940 блоками цифровой обработки сигналов и 96 приемопередатчиками, поддерживающими скорости 11,2 и 28 Гбит/с. Это семейство обеспечивает максимальную рабочую частоту для создаваемых проектов. Для задач, сконцентрированных на цифровой обработке сигналов, предназначено семейство Kintex-7, содержащее существенно меньше высокоскоростных приемопередатчиков, что позволяет снизить цену по сравнению с Virtex-7, но до 2000 блоков для цифровой обработки сигналов. Для проектов, требующих минимальной стоимости микросхем, предназначено семейство Artix-7, однако рабочая частота в нем почти в два раза ниже.

Интересным продуктом является семейство Zynq-7000 – гибрид двухъядерного процессора ARM Cortex-A9 и матрицы логических ячеек, основанной в разных вариантах микросхем Zynq на схемотехнике Artix или Kintex. Таким образом, на одном кристалле будут совмещены популярный сегодня процессор ARM и реконфигурируемая логика, способная обеспечить производительность до 900 GMAC/с, что более чем в 1000 раз превышает производительность процессорного ядра.

По цене плата на базе Spartan-6 вполне сопоставима с видеокартами верхнего ценового диапазона и может быть установлена в слот PCI Express любого компьютера. Однако без разработки каких-то конкретных конфигураций FPGA для пользователя не произойдет никаких изменений. Набор таких конфигураций для различных плат можно предполагать перспективой ближайшего будущего, при наличии благоприятной ситуации на рынке и интереса к такой технологии у широкого круга потребителей. Важно, что платы универсальных ускорителей на базе FPGA уже приближаются к приемлемому для компьютерного оборудования ценовому диапазону.

Средства разработки

Разработка проектов для FPGA не тривиальна – напрямую перенести некий код на языке Си в чип не получится. Основные инструменты проектирования на сегодняшний день – это низкоуровневые языки описания аппаратуры (Hardware Description Language, HDL), описывающие не порядок действий при вычислениях, а список соединений компонентов. Это является определенным барьером (впрочем, больше психологическим) для программистов, затрудняющим процесс освоения такой технологии. Не всегда оказывается легко сконфигурировать FPGA так, чтобы она выполнила сотни, и даже тысячи действий за один такт, а ведь для ее эффективного использования необходимо проектировать устройство именно в таком стиле, поэтому в области программируемой логики сейчас активно исследуются средства описания схем, повышающих эффективность разработчика. К таким средствам можно отнести библиотеки готовых компонентов – IP-ядер (Intellectual Property – "интеллектуальная собственность"), представляющих собой уже разработанные описания на HDL, сопровождаемые проектными ограничениями – указаниями по оптимальному размещению компонентов на кристалле. Ориентация на IP-ядра позволяет быстро собрать проект из «крупных кубиков» – цифровой фильтр или декодер для видео требуют только настройки в графическом интерфейсе САПР, а не разработки с нуля. Сюда же можно отнести надстройки для САПР – например, Xilinx предлагает отдельные среды для разработки систем на базе процессоров и для проектирования систем цифровой обработки сигналов. В последнем случае используется пакет Matlab, который с помощью модулей, добавляемых Xilinx, способен сгенерировать HDL из блок-схемы.

Другим направлением повышения уровня разработки является применение более абстрактных языков представления схемы – переход от HDL к языкам высокого уровня. Такие языки скрывают низкоуровневые особенности функционирования кристалла, позволяя описывать схему на языке, близком к Си. В качестве примера можно привести System C, Catapult C или систему AutoESL, недавно анонсированную Xilinx в качестве альтернативного маршрута проектирования систем на базе FPGA.

Кому это нужно?

Чем и кому могут помочь FPGA сегодня? Программируемая логика позволяет подойти к выпуску микроэлектронной продукции не только конструкторским организациям, но и энтузиастам. Схема на языке описания аппаратуры пригодна для реализации и в FPGA, и в специализированной микросхеме с металлическими соединениями – собственно, FPGA и являются штатными «испытательными стендами» при проектировании интегральных микросхем. Платы на основе FPGA вполне доступны по цене и позволяют получить работающий прототип микросхемы даже в домашних условиях.

Уже состоявшимся направлением использования FPGA является создание на их основе высокопроизводительных систем, к ним относятся, например, масштабируемые вычислительные кластеры, производимые НИИ многопроцессорных вычислительных систем Южного федерального университета или реконфигурируемая вычислительная система РВС-5, установленная в МГУ, которая содержит 1280 FPGA семейства Virtex-5 и 100 Гбайт памяти, обеспечивающие пиковую производительность 5 TFLOPS при потребляемой мощности 24 кВт. Система РВС-5 позволяет строить специализированные вычислители, свободные от недостатков кластеров на основе процессоров x86, – нет необходимости организации совместного доступа к данным. В каждом кристалле можно построить довольно сильно связанные схемы, способные обмениваться данными гораздо интенсивнее, чем процессоры x86. Однако препятствием является отсутствие готовых решений для автоматического ускорения вычислений, что, впрочем, является точкой приложения сил для исследовательских и конструкторских организаций.

Плата на базе Spartan-6 относится к первой волне изделий, которые могут быть установлены непосредственно в пользовательский компьютер и при этом имеют цену, сопоставимую с ценой мощной видеокарты. Проблема здесь та же – без загруженной конфигурации такая плата ничего не изменит. Будут ли в ближайшем будущем компьютеры настраиваться под конкретную задачу, зависит уже не от технологов, а от разработчиков конфигураций для FPGA.

Илья Тарасов (ilya.tarasov@inlinegroup.ru) — ведущий специалист КТЦ «Инлайн груп» (Москва).