Завершились государственные испытания универсального высокопроизводительного российского компьютера «Эльбрус-3М». С большим опозданием Россия, вслед за США и Японией, создала универсальный микропроцессор. Как полагают его создатели, системы «Эльбрус» смогут найти свою специфическую нишу в отечественном ИТ-ландшафте.

Завершились государственные испытания универсального высокопроизводительного российского компьютера «Эльбрус-3М». С большим опозданием Россия, вслед за США и Японией, создала универсальный микропроцессор. Как полагают его создатели, системы «Эльбрус» смогут найти свою специфическую нишу в отечественном ИТ-ландшафте.

В конце 2007 года в МЦСТ прошли испытания компьютера «Эльбрус-3М», использующего микропроцессоры собственной архитектуры, обладающего рядом уникальных свойств: высокой логической скоростью с низким энергопотреблением за счет явного параллелизма операций, полной и эффективной двоичной совместимостью с архитектурой x86 на базе скрытой системы двоичной трансляции и средствами защищенного исполнения программ на базе аппаратных тегов.

Рождение новой архитектуры

Архитектурная линия микропроцессоров «Эльбрус» берет свое начало от многопроцессорных вычислительных комплексов «Эльбрус-1» и «Эльбрус-2», созданных соответственно в 1980-м и 1985 годах. До начала 90-х годов десятипроцессорный МВК «Эльбрус-2» был самой высокопроизводительной машиной в СССР. Программирование этой системы велось только на языках высокого уровня, а средства поддержки защищенного исполнения выполнялись на базе не имеющего аналогов в мире подхода с использованием аппаратных тегов, что значительно повышало надежность и сокращало цикл разработки программ. Продолжением этой линии должен был стать 16-процессорный МВК «Эльбрус-3», работа над которым началась в 1986 году.

В отличие от «Эльбрус-1» и «Эльбрус-2», в которых применялся суперскалярный принцип распараллеливания операций (до двух операций за такт), в процессоре «Эльбрус-3» было реализовано явное управление параллелизмом операций. Эта система разрабатывалась на больших интегральных схемах, и один процессор занимал целый шкаф. Первые процессоры были изготовлены в начале 1991 года, но через год проект был остановлен.

В новых рыночных условиях воплотить идеи, заложенные в архитектуру «Эльбруса-3», можно было, только обеспечив совместимость с какой-либо распространенной микропроцессорной архитектурой. После создания в 1992 году компании МЦСТ в течение четырех лет велась работа с Sun Microsystems над микропроцессором с явным параллелизмом и с возможностью исполнения двоичных SPARC-приложений под управлением операционной системы Solaris на базе технологии двоичной трансляции, однако в 1996 году Sun Microsystems прекратила свое участие в проекте.

Следующий микропроцессор, получивший название Elbrus-2000 (E2k), разрабатывался полностью совместимым с IA-32 на базе системы динамической двоичной трансляции любых программ, включая операционные системы [1,2]. Кроме того,

в архитектуре E2k получили дальнейшее развитие аппаратные средства поддержки защищенного исполнения программ.

С октября 2000 года возобновилось государственное финансирование разработки вычислительного комплекса «Эльбрус-3М» на базе микропроцессора «Эльбрус», в котором был воплощен весь архитектурный и программный задел проекта E2k. На доработку и верификацию архитектуры и логики работы, а также на физическое проектирование микропроцессора ушло четыре года – в мае 2005 года был изготовлен первый микропроцессор. К этому сроку на ПЛИС (программируемые логические интегральные схемы) были спроектированы контроллеры памяти и внешних устройств и изготовлен двухпроцессорный «Эльбрус-3М».

Явный параллелизм операций

Параллелизм операций – наиболее универсальный вид параллелизма, использование которого позволяет существенно повысить производительность последовательных программ: в 6-8 раз для целочисленных программ со сложной логикой управления и более чем в 20 раз для программ, где большая часть работы выполняется над регулярными данными в циклах, а параллелизм сдерживается темпом доступа в память.

Во всех современных микропроцессорах (Intel Core 2, AMD Opteron, IBM Power 6) для повышения производительности применяется суперскалярный принцип распараллеливания операций. При исполнении программы ее операции помещаются в специальный буфер, аппаратно анализируются зависимости между ними, переименовываются регистры для устранения ложных зависимостей, вычисляются условия готовности и выполняется назначение (планирование) устройств для выполнения. В архитектурах с явным параллелизмом операций, к которым относятся микропроцессоры «Эльбрус» и Intel Itanium, анализ зависимостей между операциями, планирование их исполнения и распределение регистров выполняются при компиляции программы. Тем самым микропроцессор освобождается от значительной части функций суперскалярных архитектур, вследствие чего он потребляет меньше энергии и в нем можно использовать больше параллельно работающих устройств исполнения операций. Всю работу по распараллеливанию операций берет на себя оптимизирующий компилятор.

В микропроцессоре «Эльбрус» (техпроцесс – 130 нм, тактовая частота – 300 МГц) для параллельного запуска операций используется командное слово, размер которого может достигать 64 байт. По своим пиковым характеристикам производительности –

23 операции за такт для 64-разрядных вычислений – «Эльбрус» почти вдвое превосходит все существующие универсальные микропроцессоры. Средства векторизации, реализованные в компиляторе, позволяют задействовать аппаратные команды над упакованными данными, повышая производительность программ, использующих 32-, 16- и 8-разрядные данные. По темпу поступления данных из памяти в пересчете на одну 64-разрядную операцию – 7 байт для кэш-памяти и 2 байт для оперативной памяти на процессор – двухпроцессорный вычислительный комплекс «Эльбрус-3М», работающий на общей памяти с симметричным доступом, сравним с лучшими суперкомпьютерами.

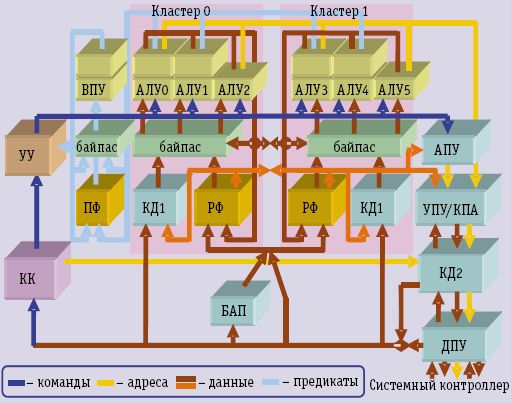

Структура микропроцессора «Эльбрус» (рис. 1) почти повторяет E2k. Шесть арифметико-логических устройств разделены между двумя кластерами с собственной копией регистрового файла и кэш-памяти первого уровня, причем содержимое обеих копий совпадает. Для повышения параллелизма на некоторых арифметико-логических устройствах можно запустить пару зависимых операций. Использование однобитовых предикатов приводит к сокращению операций передачи управления, а спекулятивное выполнение операций позволяет избавиться от ложных зависимостей и тем самым повысить производительность, достигая времени выполнения критических путей для программ со сложной логикой управления и ограниченным параллелизмом. Устройство вычисления адресов и предварительной асинхронной подкачки данных позволяет скрыть задержки, нарушающие подготовленное компилятором планирование операций, а аппаратная поддержка программной конвейеризации циклов позволяет полностью загрузить наиболее критические устройства исполнения.

Рис. 1. Структурная схема микропроцессора «Эльбрус». ВПУ – устройство вычисления предикатов; АЛУ – арифметико-логические устройства; УУ – устройство управления; байпас – устройство, ускоряющее передачу данных; АПУ – устройство асинхронной подкачки данных из памяти; ПФ – предикатный файл; КД1 – кэш данных первого уровня; РФ – регистровый файл; УПУ/КПА – устройство преобразования виртуальных адресов в физические, включая кэш адресов; КК – кэш команд; КД2 – кэш данных второго уровня; БАП – буфер для асинхронной подкачки данных; ДПУ – устройство организации доступа в память

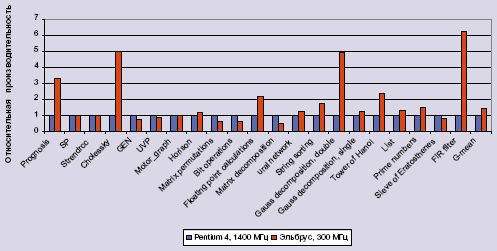

Производительность микропроцессора «Эльбрус» составляет 16/8 GFLOP/ГГц для 32-/64-разрядных вещественных операций, а отношение производительности к мощности -- 400 MFLOP/Вт, что является прямым следствием использования явного параллелизма операций с передачей функций их распараллеливания оптимизирующему компилятору. Это почти вдвое выше аналогичных параметров универсальных микропроцессоров. Проведенные в ходе государственных испытаний замеры производительности на программных системах, предоставленных различными организациями, показали, что оптимизированные компилятором коды исполняются на 300-мегагерцевом «Эльбрус-3М» в среднем в 1,44 раза быстрее, чем на Pentium 4/1,4 ГГц (рис. 2).

Рис. 2. Сравнительная производительность «Эльбрус-3М1» с микропроцессором «Эльбрус»/300 МГц и Pentium 4/1400 МГц на задачах пользователей

Двоичная совместимость с IA-32

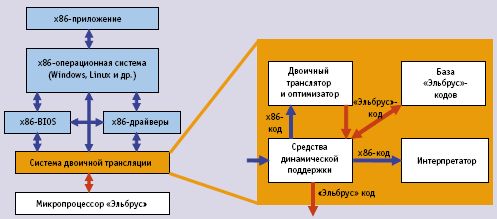

«Эльбрус-3М» обеспечивает полную двоичную совместимость с архитектурой IA-32 на базе технологии скрытой (невидимой пользователю) динамической двоичной трансляции со специальной аппаратной поддержкой (рис. 3). Основные компоненты данной технологии:

-

интерпретатор кодов IA-32, работающий при первом исполнении и добавляющий средства мониторинга;

-

двоичный транслятор, перекодирующий коды IA-32 в коды микропроцессора «Эльбрус», используя для этого несколько уровней оптимизации;

-

база кодов, обеспечивающая хранение и накопление оптимизированных кодов;

-

система динамической поддержки, обслуживающая весь этот процесс.

Рис. 3. Схема работы динамической, невидимой пользователю двоичной трансляции

Для ускорения исполнения оптимизирующая трансляция запускается на свободном процессоре, а хорошо оптимизированные части кода сохраняются в базе кодов и при повторном исполнении той же программы используются без потери времени на их перекомпиляцию и оптимизацию.

Современные суперскалярные микропроцессоры Intel и AMD аппаратно преобразуют сложные команды переменной длины в более простые микрооперации. Затем анализируются зависимости, назначаются регистры и планируется выполнение микроопераций, а для некоторых реализаций (Pentium 4) формируется трасса микроопераций, которая помещается в специальную скрытую память (кэш трасс) для повторного использования. Такую реализацию вполне можно было бы назвать аппаратным двоичным транслятором. При использовании программно-аппаратной двоичной трансляции перекодировка двоичных кодов исходной архитектуры в функционально эквивалентные коды целевой архитектуры, анализ зависимостей, набор регионов планирования, назначение регистров и планирование операций исключаются из аппаратуры. Однако в эту трансляцию встраивается важный набор средств обеспечения эффективности и надежности системы двоичной трансляции [3], что позволяет достигать высокой логической скорости (времени выполнения при одинаковых тактовых частотах) для программ в кодах IA-32. На всех задачах пакета SPECfp95 производительность «Эльбрус-3М»/300 МГц в среднем превосходит производительность Pentium II/300 МГц в 1,75 раза и на 17% выше, чем у Pentium III/450 МГц. На более широком классе задач производительность ВК «Эльбрус-3М» при исполнении кодов IA-32 сравнима с производительностью процессоров Pentium II, Pentium III и Pentium IV, работающих в диапазоне частот 300-1500 МГц.

Сегодня на «Эльбрус-3М» работает около 20 операционных систем в кодах IA-32: MS-DOS, Windows, Linux, FreeBSD, QNX и др. Под управлением этих операционных систем на платформе «Эльбрус-3М» работает около тысячи приложений, в том числе компьютерные игры, программы из состава пакета Microsoft Office, видеоролики, программы компрессии данных, драйверы внешних устройств. Все это свидетельствует о надежности и полноте системы двоичной трансляции.

Средства защищенного исполнения программ

На всех современных вычислительных системах адреса и данные неразличимы, что дает большую свободу программистам при использовании ассемблеров и языков типа Си и С++, но делает данные и сами программы незащищенными от программных ошибок и злонамеренных проникновений через указатели, нарушающие языковые границы объектов, «зависшие» ссылки на уничтоженные объекты и доступ в приватные области данных.

В архитектуре микропроцессора «Эльбрус» в качестве адресов используются специальные структуры данных – дескрипторы, описывающие весь объект (переменную, массив) и текущее положение указателя внутри него, а для типизированных объектов – еще и информацию о типе и правах доступа к полям [4]. Эта структура данных защищена аппаратными тэгами – двумя дополнительными битами, которыми снабжается каждое 32-разрядное слово в памяти машины, а сами биты хранятся в кодах коррекции памяти. Таким образом, аппаратура отличает любое числовое значение от дескриптора и запрещает использование чисел в качестве адресов для обращения в память. Дескрипторы не могут быть «сконструированы» программистом и формируются аппаратными командами при выделении памяти в стеке процедур, а вне стека – операционной системой.

Защита объектов с помощью дескрипторов дополнена действенным механизмом межмодульной защиты. Аппаратура гарантирует, что объекты (данные и функции), не входящие в интерфейс модуля, не могут быть прочитаны или модифицированы из других модулей. Для типизированных объектов при этом гарантируется невозможность доступа к приватным данным объекта, кроме как через методы соответствующего типа (класса). Межмодульная защита работает для каждой функции, а модулем является единица компиляции (для Си) или класс (для С++).

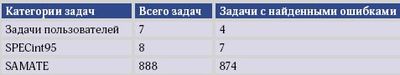

Таким образом, «Эльбрус-3М» предоставляет средства для создания надежного программного обеспечения, поскольку при защищенном исполнении обнаруживаются причины «неопределенного» (на обычных машинах) поведения программ, а опасные и сложные ошибки (нарушение границ объектов, использование неинициализированных данных, опасных конструкций языка или опасных отклонений от стандарта языка) хорошо локализуются. Эти возможности были продемонстрированы на государственных испытаниях «Эльбрус-3М» при переносе и защищенном исполнении задач пакетов SPEC95 и SAMATE (собранные по всему миру ошибочные фрагменты широко распространенных программ).

Развитие микропроцессоров с архитектурой «Эльбрус»

Развитие микропроцессорной архитектуры «Эльбрус» предполагается вести в направлении создания системы на кристалле, увеличения числа процессорных ядер и повышения тактовых частот путем включения большего числа блоков, реализованных с использованием технологии полностью заказного проектирования, а также развития технологии эффективной совместимости с архитектурами IA-32 и Intel 64 [5].

В 2009 году завершается разработка микропроцессора «Эльбрус-S» (техпроцесс – 90 нм, тактовая частота – 500 МГц), представляющего собой систему на кристалле. В него встроены каналы доступа в память, включая контроллеры DDR2 с общей пропускной способностью 8 Гбайт/с, а для создания многопроцессорных систем на общей памяти – три дуплексных канала когерентного обмена с другими процессорами и канал доступа к внешним устройствам. Пиковая производительность микропроцессора возрастет пропорционально тактовой частоте, а производительность на реальных задачах – в два раза по сравнению с микропроцессором «Эльбрус».

Параллельно начата реализация гибридного микропроцессора, содержащего два ядра с архитектурой «Эльбрус» и четыре специализированных ядра для обработки сигналов (техпроцесс – 90 нм, тактовая частота – 600 МГц). Пиковая производительность этого микропроцессора превысит 30 GFLOPS.

В планах МЦСТ – освоить технологические нормы 65, 45 и 32 нм, поднять тактовую частоту микропроцессора выше 2 ГГц и увеличить число ядер в нем до 16. Это позволит получить универсальный микропроцессор терафлопного диапазона, а за счет развития линии гибридных микропроцессоров поднять производительность еще на порядок. При проектировании предполагается использовать технологию энергосбережения.

От ПК до суперкомпьютера

Совместимость архитектуры «Эльбрус» с IA-32 и Intel 64 открывает хорошие перспективы для широкого внедрения. За счет преимущества в логической скорости архитектура «Эльбрус» с ростом тактовых частот микропроцессоров сможет развиваться не как абсолютно новая, а как совместимая с платформой Intel. Перекомпиляцию программ с целью получения дополнительной производительности для наиболее критических применений можно будет выполнять постепенно, по мере необходимости.

Внедрению компьютеров с архитектурой «Эльбрус» в качестве ПК, кроме совместимости с архитектурой Intel, будет способствовать их удешевление, которое при массовом выпуске станет прямым следствием сокращения количества чипов в компьютере за счет создания многоядерных систем на кристалле.

Серверы с архитектурой «Эльбрус» будут опираться на многопроцессорность с использованием когерентной общей памяти. Предполагается довести количество процессорных ядер в одном сервере до 1024, используя для этого до 64 процессоров.

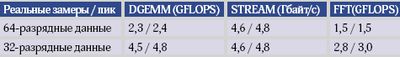

Многопроцессорный сервер с когерентным доступом в память может рассматриваться как узел для построения суперкомпьютера. «Эльбрус-3М» демонстрирует на задачах из области суперкомпьютеров производительность, близкую к пиковой (таблица 2), что делает вполне реальной возможность создания российского суперкомпьютера на базе микропроцессоров «Эльбрус» – при объединении в одном комплексе от 64 до 256 серверов он сможет достичь производительности петафлопного диапазона [6].

Повышение производительности программ, исполняемых в виде двоичных кодов IA-32 за счет совершенствования технологии двоичной трансляции, повышение производительности переносимых программ за счет совершенствования компилятора с языков Си, С++ и Фортран и развитие ОС Linux, поддерживающей защищенное исполнение программ и работу в реальном времени, придадут дополнительную привлекательность платформе «Эльбрус».

1.Михаил Кузьминский. Отечественные микропроцессоры: Elbrus E2K // Открытые системы.СУБД.–1999.– № 5-6.

2. Babayan B.A. Main principles of E2k architecture // Free Software Magazine. 2002, No. 2.

3. Волконский В.Ю. Оптимизирующие компиляторы для архитектуры с явным параллелизмом команд и аппаратной поддержкой двоичной совместимости // Информационные технологии и вычислительные системы. – 2004. – № 3.

4. Груздов Ф.А., Сахин Ю.Х. Архитектурная поддержка типизации данных//Информационные технологии и вычислительные системы. – 1999.– №1.

5. Ким А.К.Развитие архитектуры вычислительных комплексов серии «Эльбрус»//Сб.научных трудов ИТМ и ВТ/Под ред. Калина С.В.– М: ИТМ и ВТ им. С.А. Лебедева РАН. –2008. – № 1.

6. Леонид Черняк. HPC: Факторы влияния // Открытые системы.СУБД.–2007.–№10.

Владимир Волконский, Федор Груздов, Александр Ким, Юлий Сахин ({vol,fg,kim,yuli}@mcst.ru) – сотрудники «ИНЭУМ им. И.С. Брука» и «МЦСТ» (Москва).