.jpg) |

|

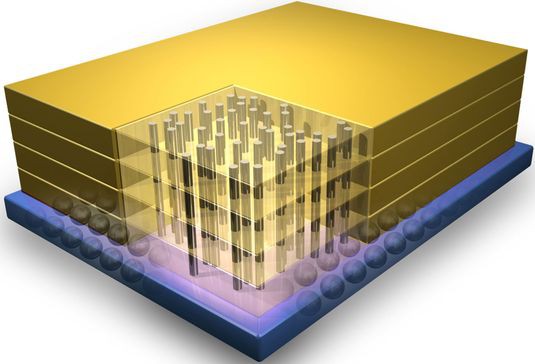

Разработчики Hybrid Memory Cube изменили традиционнцю структуру DRAM. Источник: Micron |

Компании Micron, Samsung и Hynix возглавляют проект, поддерживаемый консорциумом Hybrid Memory Cube Consortium (HMC). Решение Hybrid Memory Cube позволяет объединять в стек кристаллы энергозависимой памяти, размещаемые поверх контроллера DRAM.

Память подключается к контроллеру с помощью относительно новой технологии VIA (Vertical Interconnect Access), позволяющей устанавливать вертикальные электрические соединения через кремниевую пластину.

Майк Блэк, главный разработчик технологической стратегии Hybrid Memory Cube в компании Micron, указал, что создатели HMC пересмотрели традиционную структуру DRAM.

«Логику функционирования DRAM мы интегрировали в чип, монтируемый у подножия трехмерного стека, – указал Блэк. – Такое решение позволяет использовать преимущества высокопроизводительных транзисторов не только при взаимодействии с оперативной памятью, но и для эффективной организации высокопроизводительных вычислений через канал основного процессора. Таким образом, логический уровень одновременно выполняет роль основного интерфейсного соединения и контроллера памяти, к которому подключаются микросхемы DRAM».

Память разбивается на 16 разделов, каждый из которых соединен с контроллером двумя каналами ввода-вывода. У каждого из двух существующих прототипов Hybrid Memory Cube центральной системе доступны 128 или 256 банков памяти.

Первые спецификации трехмерных чипов емкостью 2 и 4 Гбит обеспечивают пропускную способность 160 Гбит/с в каждом из направлений, тогда как общая пропускная способность памяти DDR3 составляет 11 Гбит/с, а памяти DDR4 – от 18 до 20 Гбит/с.

.jpg) |

|

Подключение Hybrid Memory Cube к процессору |

По словам директора исследовательской компании Objective Analysis Джима Хэнди, технология Hybrid Memory Cube позволит решить ряд очень важных вопросов. Современные чипы DRAM обременены множеством дополнительных схем, разъемов и каналов связи с другими элементами, которые обеспечивают передачу данных по шине на гигагерцевых скоростях и потребляют большое количество энергии.

Технология HMC позволяет оснащать микросхемы DRAM только крошечными соединениями TSV, испытывающими намного меньшую нагрузку на коротких расстояниях. Связь с процессором и другими устройствами поддерживает логическая схема в нижней части стека. «Новый интерфейс работает в 15 раз быстрее стандартных элементов DRAM, позволяя при этом сократить энергопотребление на 70%, – указал Хэнди. – Ценность такого решения состоит в том, что оно устраняет все барьеры на пути дальнейшего увеличения производительности DDR3 и DDR4.

Вместо нескольких разъемов DIMM (число которых может варьироваться от одного до четырех) на материнской плате размещается лишь один коннектор Hybrid Memory Cube, тем самым сокращается число интерфейсов с центральным процессором.

Спецификации HMC определяют два физических интерфейса с центральным процессором: короткий и сверхкороткий. Короткий интерфейс аналогичен большинству технологий, используемых в современных материнских платах, где расстояние от памяти до процессора находится в пределах 20-25 см. Технология предназначена главным образом для транспортировки данных и должна способствовать доведению пропускной способности до 15-28 Гбит/с на каждый канал в четырехканальной конфигурации.

«Первый коммерческий продукт должен появиться во второй половине текущего года и будет поставляться в довольно большом корпусе, поскольку расстояние между контактами не может быть меньше 1 мм, – сообщил Блэк. – В результате логический чип и кристалл DRAM, занимающие всего 100 кв. мм, мы вынуждены размещать в корпусе, размеры которого существенно превышают размеры находящихся в нем микросхем».

Сверхкороткие соединения отличаются низким энергопотреблением, высокой скоростью передачи данных и поддержкой FPGA и ASIC. Расстояние от памяти до процессора находится в интервале от 3 до 8 см, а пропускная способность составляет 15 Гбит/с на канал.

«Такое решение оптимизировано для обмена сигналами очень малой мощности с модулями, объединяющими несколько микросхем, – пояснил Блэк. – При этом корпус становится гораздо компактнее, а расстояние между его контактами не превышает 300 микрон».

Стоимость трехмерных модулей DRAM оказывается выше, чем у их предшественников, однако решение с аналогичной пропускной способностью на базе стандартных модулей DRAM обошлось бы еще дороже.

«Если вы попытаетесь добиться такой же производительности с использованием традиционной технологии DRAM, во многих случаях общая стоимость решения Hybrid Memory Cube окажется значительно ниже», – подчеркнул Блэк.

.jpg)