На сегодня память стандарта GDDR3 составляет 90% элитного рынка графических устройств, но уже к 2011 году положение изменится: наберет силу GDDR5, способный стать следующим основным графическим стандартом DRAM и вывести пропускную способность памяти для графических приложений на новый уровень. По расчетам Mercury Research, к 2011 году GDDR5 будет составлять 90% рынка, что составит 1,49 млрд. долларов только в сфере компьютерных приложений. GDDR5 будет предназначаться для графических подсистем персональных компьютеров, игровых консолей, элитных потребительских (цифровые телевизоры и приставки) и сетевых приложений.

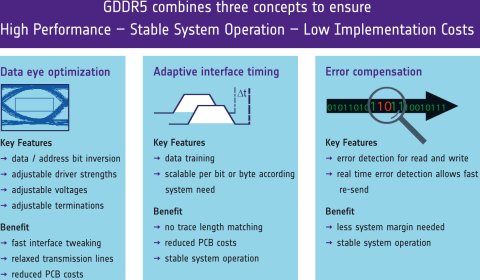

Пропускная способность памяти – главное требование к постоянно совершенствующейся трехмерной графике компьютеров и игровых консолей. Статистика показывает, что каждый год она увеличивалась примерно на 30%. Вскоре закончатся работы в рамках программы JEDEC (Объединенная программа экспериментальной разработки электронных компонентов) по GDDR5, потребляющему меньше электроэнергии и способному передавать данные со скоростью 20Гбит/с, что почти в два раза больше, чем предлагают современные модули GDDR3. GDDR5 включает три основные компонента, обеспечивающие более высокую производительность, стабильную работу системы, малую себестоимость и низкое потребление энергии: чистота сигнала с использованием инверсии разрядов адреса/данных, регулируемая мощность драйвера, напряжения и оконечных схем; адаптивный интерфейс с масштабируемой подготовкой данных; компенсация погрешности при точном определении времени сигнала ошибки. Эти характеристики обеспечивают быструю подстройку интерфейса, снижение стоимости электронных печатных плат и более стабильную работу системы.

В GDDR5 SGRAM компании Qimonda совершенствует применявшийся ранее способ несимметричной подачи сигналов до уровня очень высоких частот. GDDR5 продолжает осуществление проверенного на практике высокоуровневого прекращения подачи сигнала, при сохранении напряжения драйверов виртуального устройства Vdd и Vddq на уровне 1,5В, с возможностью дальнейшего потенциального снижения напряжения. Интерфейс GDDR5 оптимизирован для 32 и 64-разрядных каналов. Генератор тактовых импульсов, команды и адреса могут перераспределяться между двумя устройствами, в то время как управляющие данные передаются по двухточечному маршруту для обеспечения высокой скорости передачи данных.

Инверсия данных на линиях

Инверсия данных на линиях (DBI) – это технология снижения числа передаваемых нулей. Данные инверсируются, если более 50% информационных двоичных разрядов внутри байта представляют нули. Поскольку трансмиссионные подводящие линии GDDR5 обладают высоким уровнем штатного завершения, уменьшение количества сигнальных магистралей, действующих на низшем (нулевом) уровне, приводит к снижению распыления энергии в согласующем резисторе и выводимых драйверах. Кроме того, инверсия данных улучшает качество сигнала за счет сокращения случайных помех, вызванных шумом. GDDR5 обеспечивает инверсию адресной шины (ABI) так же эффективно, как DBI, что тоже снижает энергопотребление и шумы на адресных магистралях.

Подача сигнала

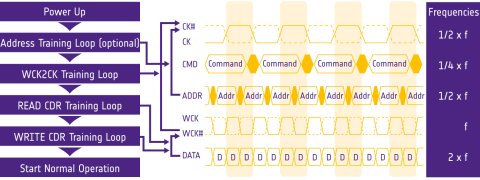

Регулировка сигнала представляет собой одну из самых больших проблем в высокоскоростных приложениях. Технология подачи сигнала GDDR5 предоставляет системным компоновщикам надежные, легко применимые решения. Также она дает возможность выстраивать в последовательный ряд сигналы и синхроимпульсы относительно друг друга. Подача сигнала представляет собой фазу согласования различных сигналов. GDDR5 работает с двумя различными типами синхроимпульсов: командный сигнал (CK), куда отсылаются и входящие адреса и команды, и пишущий синхроимпульс, где записываются и читаются данные. Подача синхроимпульсов и данных осуществляется в три этапа: подача адресных данных (настраивает адресную шину на командный синхроимпульс), настройка WCK на CK (настраивает пишущий синхроимпульс на командный синхроимпульс) в детекторе дисперсной фазы DRAM и, наконец, подача сигнала (окончательно переводит данные в соответствующий пишущий синхроимпульс). По итогам подачи все сигналы и синхроимпульсы выстраиваются в памяти, как показано на рисунке ниже.

Адаптация

Технология GDDR5 SGRAM обладает несколькими характеристиками, которые позволяют контроллеру наилучшим образом привести в соответствие показатели входа и выхода устройства с фактическим полным сопротивлением и тем самым улучшить исходные данные для надежной передачи информации. Это следующие характеристики:

-

автоматическая калибровка процессов, коррекция параметров температуры и напряжения;

-

контролируемая программным обеспечением, регулируемая сила накопителя;

-

контролируемая программным обеспечением оконечная нагрузка, равная сопротивлению, при передаче данных, адресов и команд;

-

контролируемые программным обеспечением параметры эталонного напряжения на входе.

Определение сигнала ошибки

Новой отличительной особенностью GDDR5 является возможность распознавать искажения при передаче, возникающие на высокоскоростных сигнальных магистралях. Поскольку графические системы хранят все большее количество кодов в DRAM, детектирование сигнала ошибки приобретает очень большое значение. Это связано с тем, что ошибка на произвольном разряде при любой высокоскоростной передаче данных приведет к недопустимым системным сбоям. В GDDR5 передаваемые данные сохраняются посредством цикла квантовых вычислений с использованием алгоритма, точно установленного для высококачественной среды передачи данных, таких как сети АТМ. Алгоритм распознает все единичные и двойные ошибки со стопроцентной точностью. Когда контроллер DRAM распознает ошибку, команду, вызвавшую эту ошибку, можно повторить еще раз. Распознавание ошибки может использоваться для инициирования повторного тренинга канала передачи данных, что позволяет системе динамично приспосабливаться к меняющимся условиям, таким, как изменение температуры и напряжения.

Ядро памяти

Архитектура ядра GDDR5 оптимизирована для поддержания высокого диапазона частот интерфейса, а также одновременного обеспечения низкого времени ожидания прямого доступа в ядро памяти. Это достигается благодаря наличию 16 информационных банков и предварительной выборке 8 из них, что превращает GDDR5 в стандарт с исключительно высокой производительностью.

Базовыми компонентами ядра являются 8 банков на 512 Мбит памяти GDDR5 и 16 банков на 1 или 2 Гбит, предварительная выборка 8 и фиксированный размер страницы 2кВ для всех плотностей записи.

Управление энергопотреблением

GDDR5 разработана таким образом, чтобы обеспечить потребление энергии только в случае реальной необходимости. Следующие характеристики и методики специально применяются в GDDR5 для обеспечения управления энергопотреблением по требованию:

-

чрезвычайно широкий диапазон синхронизирующей частоты и скорости передачи данных;

-

доступ к многоступенчатому завершению работ по требованию;

-

режимы пониженной мощности для ядра DRAM;

-

низкое потребление энергии 1,5 В;

-

инверсия разрядов данных и адресов;

-

режимы выключения питания и самообновления.

Технология GDDR5 позволяет системе оперативно изменять скорость передачи вводимых и выводимых данных памяти в соответствии с рабочей нагрузкой. Скорость вводимых и выводимых данных в GDDR5 может колебаться от 5 Гбит/с до 200 Мбит/с (при синхронизирующей частоте 50 МГц).

В зависимости от нагрузки, набор рабочих параметров может меняться, чтобы постоянно обеспечивать работу при наименьшем возможном энергопотреблении. На более низких частотах ФАПЧ (система фазовой автоподстройки частоты) может выключаться, и интерфейс GDDR5 может быть переведен в стробирующий режим с малой мощностью. В этом случае графический процессор может выключать синхронизатор восстановления данных, тем самым снижая энергопотребление. Для упорядочивания данных в стробирующем режиме DRAM вместе с данными посылается строб-импульс через контакт управления экономичным распределением нагрузки (EDC). Помимо масштабирования частоты входа и выхода, ядро DRAM GDDR5 предусматривает режим малой мощности для работы на низких частотах.

Он задается набором разрядов малой мощности из контроллера. Прекращение сигнала необходимо для соответствия полному сопротивлению трансмиссионных каналов и улучшения качества сигнала. Однако и при прекращении сигнала происходит потребление энергии. При низкой скорости передачи данных подача сигналов требует резерва, который позволяет запускать систему с частично подогнанным межэлектродным сопротивлением завершения передачи сигнала. GDDR5 позволяет удвоить сопротивление на более медленных скоростях передачи данных или даже отключить его. Завершение передачи может выполняться отдельно применительно к информационной, адресной и командной шине и синхронизатору WCK для получения максимальной выгоды от энергосбережения. Возможность инверсии информационных и адресных разрядов не приводит к снижению энергии, потребляемой согласующим резистором и выводящими драйверами. Схема высокого уровня прекращения передачи сигнала предусматривает потребление энергии только в случае перевода линии передачи на низкий уровень. Поскольку инверсия разрядов данных и адресов эффективно снижает количество низких сигналов в информационной и адресной шинах, в результате снижается и общее потребление энергии системой в целом.

Об авторе: Кристоф Билгер - главный менеджер по маркетингу департамента Business Unit Graphics компании Qimonda.