Быстрый рост производительности крупнейших суперкомпьютерных инсталляций мира в последние годы в значительной мере определяется развитием кластеров, которые обычно строятся на базе универсальных высокопроизводительных микропроцессоров, применяемых и в обычных серверах. Исключения— недавно возглавлявшие этот список векторные суперкомпьютеры NEC Earth Simulator и МРР-системы с распределенной оперативной памятью IBM BlueGene— общей тенденции не меняют.

Для устойчивого прогресса на этом пути необходимо адекватное продолжение роста производительности узлов кластеров, хотя растет и число узлов в кластерах. Рост же производительности узлов до недавнего времени определялся экспоненциальным ростом производительности процессоров.

Будет ли продолжаться такое развитие и далее, и если будет, то как долго? Некоторые изменения уже произошли: процессоры стали многоядерными. Cегодня универсальные высокопроизводительные процессоры имеют по два-четыре ядра, и рост числа ядер, очевидно, будет продолжаться, причем также, возможно, по экспоненциальному закону.

Американская программа DARPA HPCS нацелена на преодоление рубежа производительности 1 PFLOPS. Формально в ней не прописаны конкретные технические решения. Однако, думается, ее реализация будет происходить скорее на традиционном пути; революционные же изменения можно ожидать лишь к 2010 году.

В Intel утверждают, что к 2015 году «на столе» (то есть в персональном компьютере) будет доступна производительность уровня 1 TFLOPS. И это будет реализовано за счет применения процессоров с десятками и больше числом ядер. Некоторые эксперименты на этом пути уже проводятся [1]. Однако единственный доступный прообраз многоядерных процессоров будущего — это, пожалуй, только что появившийся 64-ядерный Tile64 компании Tilera [2].

Cовременные процессоры

Сегодняшние процессоры для HPC (High Performance Computing, высокопроизводительные вычислительные системы) можно разделить на три группы: векторные; высокопроизводительные универсальные; специализированные, применяемые в компьютерных системах вместе с традиционными универсальными процессорами.

Векторные процессоры, ставшие знаменитыми благодаря Сеймуру Крею, сегодня интересны в первую очередь благодаря продукции японской компании NEC, которая сумела нарушить тенденцию сближения пиковой производительности векторных процессоров и универсальных процессоров. Новейшие векторные процессоры суперкомпьютера NEC SX-9 имеют пиковую производительность свыше 100 GFLOPS. В максимальной конфигурации SX-9 имеет 8192 процессора и 840 TFLOPS векторной производительности (970 TFLOPS— с учетом теоретической возможности одновременной работы скалярного блока с плавающей запятой). Таким образом, уровень в 1 PFLOPS почти достигается в рамках одного суперкомпьютера, а не кластера.

Для сравнения напомним, что лучший на сегодняшний день универсальный процессор IBM Power6 обладает производительностью раз в пять ниже— менее 20 GFLOPS. Основным архитектурным преимуществом векторных процессоров, кроме большой пиковой производительности, является высокая пропускная способность памяти. В SX-9 на четыре процессора приходится пропускная способность памяти в 2 Тбайт/с.

Столько же процессоров, сколько и SX-9, может иметь векторный Сray X1E, недавно снятый с производства. Однако его процессоры гораздо скромнее— как по пропускной способности памяти (34 Гбайт/с на процессор), так и по пиковой производительности— 18 GFLOPS. Cобственно говоря, векторные процессоры быстрее универсальных процессоров только на длинных векторах.

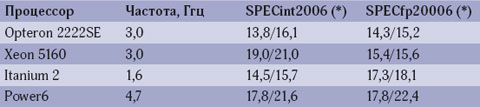

Мировым лидером производительности среди универсальных микропроцессоров является RISC-процессор Power6 с тактовой частотой 4,7 ГГц (см. табл. 1). Он обходит конкурентов и по целочисленной (SPECint2006) производительности, и по производительности с плавающей запятой (SPECfp2006), и по тактовой частоте. Кроме эффективной микроархитектуры такому успеху способствовала и передовая КМОП-технология (65 нм, SOI).

* Указано базовое/пиковое значение

Источник: www.spec.org 2007.

Однако в результатах SPECcpu2006 существенен вклад большого объема кэш-памяти старшего уровня. Так, для Itanium 2 Montecito/1,6 ГГц емкость кэша третьего уровня составляет 24 Мбайт, а для Power6— 32 Мбайт, в дополнение к 8 Мбайт второго уровня, по 4 Мбайт на ядро [4]. Для сравнения, двухъядерные Opteron имеют кэш второго уровня емкостью 2 Мбайт (1 Мбайт на ядро), двухъядерные Xeon 51XX— 4 Мбайт. Большая емкость кэша, очевидно, удорожает процессор. В случае если рабочее множество страниц приложения плохо локализуется в кэше, становится важной пропускная способность памяти. По этому показателю процессоры Intel, не имеющие встроенного контроллера памяти, уступают другим.

Наконец, важным является и показатель пиковой производительности [3]: он не только дает верхнюю границу производительности, но и служит ориентиром для некоторых задач линейной алгебры, на которых производительность приближается к пиковой (см. табл. 2). Все рассматриваемые процессоры могут выдавать четыре 64-разрядных результата с плавающей запятой за такт, и их пиковая производительность, выраженная в GFLOPS, в четыре раза выше тактовой частоты в гигагерцах. Здесь также лидирует Power6 (18,8 GFLOPS), а Itanium 2 вследствие низкой частоты с результатом 6,4 GFLOPS уступает даже Fujitsu SPARC64 VI (9,6 GFLOPS).

Увы, разработка семейства Itanium с «пост-RISC» архитектурой EPIC не увенчалась тем грандиозным техническим и маркетинговым успехом, на который претендовали ее создатели. Причины этого вовсе не обязательно искать в технической плоскости. Во многом это обусловлено выбором для Itanium характерной для RISC-процессоров маркетинговой модели с высокой торговой маржой. К тому же с какого-то момента развитие линии Itanium вообще, похоже, перестало ориентироваться на быстрый рост производительности. Это, думается, произошло при переходе от Itanium 2/Montecito к Montvale; тактовая частота процессора при этом возросла с 1,6 Ггц всего до 1,66 ГГц. В то же время семейство IBM Power демонстрирует, что RISC-подход в техническом плане вовсе не сдает своих позиций и что для достижения высокой производительности микроархитектурная реализация важнее архитектуры команд (об этом же свидетельствуют и высокие показатели производительности х86-процессоров).

Пожалуй, основным направлением повышения производительности универсальных процессоров сегодня стала многоядерность. В настоящее время число ядер в подобных процессорах невелико— два или четыре. Общий для них подход, когда в одной микросхеме соединяются ядра, в основном повторяющие бывшие одноядерные процессоры, очевидно, с ростом числа ядер быстро приведет к проблеме масштабируемости из-за ограничения пропускной способности системной шины и доступа к оперативной памяти.

Специализированные процессоры

В последние годы активно предпринимаются попытки «дополнить» универсальные процессоры специализированными аппаратными средствами для ускорения вычислений с плавающей запятой. Многие из этих средств не ориентированы исключительно на HPC, однако могут ими использоваться. Некоторые из них представляют возможности работы с векторами в модели SIMD, характерной для векторных процессоров.

Среди интересных для HPC специализированных процессоров следует упомянуть, в частности, различные программируемые графические процессоры (Graphical Processor Unit, GPU), процессоры Сell/B.E разработки IBM, Sony и Toshiba [5], ускорители вычислений с плавающей запятой типа ClearSpeed [6] и др. Некоторые из этих средств реализованы в форме отдельных плат— «акселераторов» вычислений, другие (например, Cell) интегрируют в одной микросхеме и «спецсредства», и универсальные процессоры.

Многие из этих специализированных процессоров могут производить расчеты с плавающей запятой только одинарной точности (32-разрядные), либо могут производить также и 64-разрядные вычисления, но с гораздо более низкой производительностью. Несомненно, это резко снижает привлекательность таких процессоров для HPC, где, как правило, проводятся 64-разрядные вычисления с плавающей запятой.

Cпектр архитектурных решений, используемых в такой специализированной аппаратуре, достаточно широк. Это и программируемые логические интегральные схемы (FPGA), и матричные процессоры, и архитектуры, управляемые потоком данных, в том числе потоковые процессоры. FPGA-подход уже получил достаточное распространение и применяется, например, в суперкомпьютерах Сray XD1. Однако, представляется, трудности программирования остаются серьезным препятствием на пути превращения FPGA в массовую платформу для HPC.

Видимо, несколько лучшие «HPC-перспективы» у Сell. За ними стоят мощные финансовые и технические ресурсы известных разработчиков. В настоящее время для рынка HPC в IBM предлагают серверы BladeCenter QS21, содержащие по два процессора Сell и оперативную память емкостью до 2 Гбайт. На базе таких серверов в одной стойке можно достигнуть производительности 6,4 TFLOPS. В Лос-Аламосской национальной лаборатории США совместно с IBM работают над проектом создания гибридного суперкомпьютера Roadrunner, который будет содержать 16 тыс. ядер AMD Opteron и 16 тыс. процессоров Сell при пиковой производительности 1,6 PFLOPS.

В состав процессора Cell входит ядро PowerPC c двухуровневым кэшем, блок SIMD для 128-разрядных данных и восемь блоков SPE c плавающей запятой. Каждый SPE имеет небольшую собственную локальную SRAM-память емкостью 256 Кбайт для хранения команд и данных. Блоки SPE общаются между собой через шину, к которой подсоединяются и ядро PowerPC, и контроллер памяти.

Каждый SPE может завершать на каждом такте четыре операции с плавающей запятой (32-разрядные!) типа «умножить и сложить», что эквивалентно восьми результатам с плавающей запятой за такт на один SPE, или 64 результатам за такт— на весь процессор Cell.

В настоящее время частота Cell в QS21 составляет 3,2 ГГц, чему отвечает пиковая производительность 204,8 GFLOPS— на порядок выше, чем у современных универсальных микропроцессоров. Но при работе с двойной точностью производительность падает на порядок. Кроме того, для достижения указанного уровня производительности необходимо применять программное управление локальной памятью SPE. Это опять-таки значительно обостряет проблему программирования.

Приложения, на которые ориентируется Cell, ограничены 32-разрядностью его операций: это создание цифрового контента, конструирование электронных устройств, обработка сигналов и изображений, финансовые алгоритмы, обработка сейсмоданных, задачи молекулярной динамики и др.

Примером ускорителя для операций с плавающей запятой, ориентированного на работу с х86-совместимыми процессорами, являются платы ClearSpeed Advance X620 и e620, предназначенные для работы с шинами PCI-X и PCI-E х8 соответственно. Каждая плата может работать и с одинарной, и с двойной точностью и содержит по два матричных процессора CSX600. Каждый такой процессор содержит 96 процессорных элементов, работающих на частоте всего 210 МГц, что способствует высокой производительности в расчете на 1 Вт.

Плата e620 имеет собственную память емкостью 1 Гбайт, суммарная пропускная способность обращения к внутренней памяти составляет в данном случае 200 Гбайт/с, к «внешней» памяти— 6,4 Гбайт/с [6]. При этом на матричном умножении достигается производительность 66 GFLOPS.

Этот ускоритель снабжен программными средствами разработки, включающими в себя, кроме кросс-компилятора и отладчика, библиотеку оптимизированных математических подпрограмм BLAS третьего уровня и LAPACK. Подпрограммы этой библиотеки, в свою очередь, общаются с драйвером ввода/вывода, который передает коды и данные через канал PCI-E в плату акселератора, а затем обратно— результаты расчетов. За ускорение расчетов в несколько раз здесь приходится расплачиваться необходимостью обмена данными между процессором и платой e620. Поэтому более перспективным, вероятно, являлась бы интеграция ядер типа CSX600 в единую микросхему с х86-процессором. Это отвечает общей тенденции увеличения числа процессорных ядер.

В составе команд СSX600 имеются как «монокоманды», которые исполняет один процессорный элемент, так и «поликоманды», которые могут исполнять все 96 процессорных элементов (это отвечает архитектуре SIMD).

Архитектурно близки к подходу SIMD (для него, как известно, характерно наличие команд работы с векторами) графические процессоры, которые могут применяться и для «универсальных» (General Purpose, GP) расчетов. Соответствующий подход обычно называют GPGPU (General Purpose Graphical Processor Unit). В этом направлении работают все основные игроки рынка GPU— Intel, AMD и Nvidia.

Intel не использует термин GPGPU. Весной 2007 года на форуме разработчиков Intel анонсировала продукт Larrabee, который можно рассматривать как своеобразный ответ на программируемые графические процессоры. Larrabee будет содержать много (больше восьми) ядер, в системе команд которых архитектура IA будет дополнена GPU-подобными командами. Демонстрационная версия ожидается в 2008-м, а сам продукт— в 2009 году. В Intel считают такой подход лучше, чем применение отдельных микросхем GPU, поскольку шина между процессором и GPU cтановится узким местом, в первую очередь из-за задержек передачи.

Nvidia в 2007 году объявила о создании архитектуры G80. В своей линейке продуктов Tesla [7] компания придерживается более традиционного подхода GPGPU. Компания предлагает три продукта: процессор С870 и компьютеры на его базе— настольный D870 и сервер S870. GPU содержит 128 блоков с плавающей запятой, однако только одинарной точности (64-разрядные вычисления будут поддерживаться в следующем поколении продуктов Tesla). Его пиковая производительность превышает 500 GFLOPS. Собственная оперативная память для GPU имеет емкость 1,5 Гбайт при пропускной способности 76,8 Гбайт/с, а для коммуникаций с GPU применяется канал PCI-E x16. Настольный компьютер включает в себя два GPU, сервер— четыре.

Области HPC, на которые в Nvidia ориентируют cвои продукты,— сейсмоанализ, медицинская диагностика, молекулярное моделирование. (Вероятно, в последнем случае имеется в виду все та же молекулярная динамика. Вследствие особенности ее задач для молекулярной динамики уже традиционно разрабатываются специализированные аппаратные средства— можно вспомнить, например, еще IBM MDGrape [8].)

На сегодня самым продвинутым аппаратным решением, поддерживающим вычисления с двойной точностью, выглядит GPU FireStream 9179, только что анонсированный AMD, который также работает через PCI-E x16. Надо отметить, что GPU от Nvidia (GeForce), как и GPU от ATI, вошедшей в состав AMD, основаны на потоковой архитектуре (streaming processing), которую можно считать развитием архитектурной концепции управления со стороны потока данных [9].

Эта концепция вообще отвечает не фон-неймановской архитектуре: каждая команда выполняется, как только становятся доступны ее операнды. В вершинах графа потока данных в простейшем случае располагаются команды. Недостатком такого низкоуровневого управления от потока данных являются накладные расходы на коммуникации при пересылке операндов [9].

Эффективной альтернативой такому подходу является потоковая архитектура. Здесь классическим можно считать проект Merrimac по созданию суперкомпьютера с производительностью 1 PFLOPS. В такой потоковой архитектуре в вершинах графа находятся не отдельные команды, а программы (kernels), которые могут содержать сотни команд.

Этот подход базируется на том факте, что современные КМОП-технологии сделали арифметические вычисления дешевыми, а пропускную способность— дорогой [10]. Для эксплуатации этой особенности суперкомпьютер должен базироваться на высокой «арифметической интенсивности» (отношение времени расчетов к пропускной способности) и параллелизме приложения. Последнее позволяет задействовать большое число (в Merrimac— сотни) арифметико-логических устройств (АЛУ). Через FIFO-очереди результаты из одних АЛУ могут попасть как исходные данные в другие АЛУ.Микросхема Merrimac имеет пиковую производительность 128 GFLOPS, соответственно 8192 таких микросхем позволяют достигнуть 1 PFLOPS.

Локальный характер таких потоковых программ отражается в архитектуре, содержащей большие файлы локальных регистров LRF (это способствует локальности коммуникаций в микросхеме) плюс так называемый потоковый файл регистров SRF.

Применение потоковых программ, работающих с иерархией регистров, помогает достигнуть уменьшения требуемого трафика в оперативную память на порядок. В качестве примеров использовались приложения газодинамики, гидродинамики, магнитогидродинамики и молекулярной динамики [10]. Потоки (streams) можно рассматривать как «обобщение» векторов. В Merrimac записи из потока выбираются командой загрузки потока, и одна команда может выполнять программы над одним или несколькими потоками данных.

Аналог файла векторных регистров в векторных суперкомпьютерах в Merrimac расщеплен на LRF (используемый для АЛУ-операций с тонкозернистой локальностью) и SRF— для обменов с памятью, грубозернистой локальности внешних циклов [10].

FireStream 9170, весьма перспективный с точки зрения HPC продукт, появится в первом квартале 2008 года (в AMD отмечают, что это первый в мире потоковый GPU c двойной точностью). Он содержит 32 потоковых ядра, основан на парадигме МРР и обладает пиковой производительностью 500 GFLOPS.

Как и Intel, AMD добавляет команды GPU-типа к архитектуре x86. Учитывая разнообразие аппаратных решений в рассматриваемой области и проблемы разработки программного обеспечения, интерес представляет общая программная платформа RapidMind, предоставляющая возможности высокоуровневого распараллеливания для ряда аппаратных архитектур, в том числе для GPU от Nvidia и AMD, а также Cell/B.E.

Процессоры с большим числом ядер

Остановимся теперь на процессорах, содержащих десятки ядер,— экспериментальной 80-ядерной микросхеме Intel [1] и 64-ядерном процессоре Tile64 [2] компании Tilera. Обе микросхемы характеризуются наличием межсоединения, построенного по типу двухмерной решетки. Учитывая его топологическую естественность, представляется, что в перспективе оно может стать основным и обеспечить хорошую масштабируемость по числу ядер.

Схема этого межсоединения чем-то напоминает кафельное покрытие (отдельные ядра— плитки, а межсоединение— «полоски» вокруг плиток), а потому обе компании ядра в своих процессорах именуют tile («кафель»). Впрочем, эту терминологию изобрели не они; в архитектуре предшественника Tile64— процессора Raw разработки Массачусетского технологического института— также применялся этот термин [11].

Общая архитектура перспективных многоядерных микросхем Intel предполагает решетку из ядер общего назначения и специализированных ядер. 80-ядерный прототип, TRC,— двухмерная решетка 8х10 с габаритами 22х14 мм, изготовлен по 8-слойной КМОП-технологии с типоразмером 65 нм, и каждый процессорный элемент содержит вычислительный элемент и 5-портовый неблокирующийся коммутатор, связывающий его с четырьмя соседями. Полная пропускная способность коммутатора равна 80 Гбайт/с. Вычислительный элемент содержит однотактные память данных (2 Кбайт) и команд (3 Кбайт), файл регистров емкостью 32 строки (десять портов чтения плюс четыре порта записи) и два 32-разрядных FPMAC-устройства с плавающей запятой. 9-стадийные конвейеры могут выполнять команды «умножить-и-сложить», это дает четыре результата с плавающей запятой за такт на процессорный элемент, каждый из которых использует VLIW длиной 96 бит, что обеспечивает возможность выполнения до восьми операций за такт.

Кроме того, в дальнейшем каждое ядро будет подсоединено к собственной многослойной SRAM-памяти емкостью 256 Кбайт (она будет располагаться над основной микросхемой), для чего зарезервирован пятый порт коммутатора. В TRC реализован ряд технологических инноваций по управлению электропитанием, в том числе введены новые команды, позволяющие «усыплять» или «пробуждать» любое отдельное ядро. Максимум производительности TRC равен 1,8 TFLOPS при частоте 5,6 ГГц.

Микросхему Tile64 разработчики считают относящейся к первому в мире семейству, способному масштабироваться до сотен и тысяч ядер. В отличие от TRC, Tile64— это промышленная продукция, за которой стоит свыше 40 полученных Tilera патентов.

Tilera, технологическими разработками которой руководит Ананд Агарвал, была создана в 2004 году для продвижения на рынок наработок, полученных при создании процессора Raw, над которым Агарвал трудился ранее.

Этот исследовательский процессор был, возможно, более универсальным, чем Tile64. Изготовленный по 180-нанометровой технологии IBM, он предполагал использование как параллелизма потоковых приложений, так и традиционного параллелизма на уровне команд, а также параллелизма на уровне нитей. Он показал многократное ускорение по сравнению с Pentium III, использующим КМОП-технологию того же типоразмера: от двух до девяти раз на последовательных программах, и в 10–100 раз для потоковых программ. Raw содержит 16 (4х4) программируемых ядер, каждое из которых конвейеризовано (глубина конвейера— восемь стадий) и имеет архитектуру в стиле MIPS [11].

Raw имеет частоту 425-500 МГц. Каждое ядро связано с четырьмя соседями (что заставляет считать топологию тороидальной, а не простой двухмерной решеткой. Эта сеть использует статическую маршрутизацию и имеет собственный кэш команд. Команды маршрутизатора может генерировать компилятор. Кроме статической, Raw имеет также динамические сети, в том числе сеть для доступа в оперативную память. При этом на тестах STREAM для пропускной способности памяти Raw оказался лучше даже векторного суперкомпьютера NEC SX-7 [11].

Рассмотрим другие характеристики архитектуры Tile64. Согласно некоторым источникам, для передачи данных к соседнему узлу требуется один такт. Соответствующее межсоединение, двухмерную сеть, разработчики называют iMesh (i— от intelligent). Для доставки данных самому удаленному ядру в массиве 8х8 тогда потребовалось бы 14 таких «прыжков», но если iMesh— не двухмерная решетка, а тор, реальное требуемое число прыжков меньше.

Подобно TRC, в Tile64 предусмотрены коммутаторы в каждом процессорном ядре. В компании Tilera утверждают, что iMesh обеспечивает на порядки более высокую пропускную способность, чем шина, при том, что расстояния между ядрами короче. Это способствует и сверхнизким величинам задержек.

На самом деле iMesh включает в себя пять сетей. Две из них управляются только аппаратурой и применяются для обмена данными между ядрами и оперативной памятью в случаях DMA-передачи или промахов в кэш-памяти. Три остающиеся сети могут программироваться, обеспечивая коммуникации между ядрами и с устройствами ввода-вывода. Для доступа к этим аппаратным средствам программисту доступен ряд высокоуровневых абстракций, в том числе потоковые каналы по типу сокетов или интерфейсы обмена сообщениями.

С точки зрения производительности важно, что коммуникации в iMesh осуществляются без прерывания использующих ядра приложений и что сети iMesh имеют средства буферизации.

Каждое ядро Tile64 является полнофункциональным процессором и может выполнять коды «обычной» операционной системы и приложений. Ядра содержат кэши команд и данных первого уровня, а также кэш второго уровня. Коллекция таких кэшей разных ядер может считаться общей для всех них, и эта совокупность для приложений с общим полем оперативной памяти выступает в качестве общего многомегабайтного кэша третьего уровня. Страница памяти, загруженная в кэш какого-либо конкретного ядра, может быть при этом доступна для операций типа загрузки регистров/записи в память другими ядрами.

Каждое ядро имеет полный доступ к памяти и вводу/выводу, применяет виртуальную память, используя блоки TLB, поддерживает многоуровневую систему прерываний. Система команд ядра— VLIW c шириной в три команды [11]. В процессор интегрирован не только контроллер памяти, но и два порта 10G Ethernet.

Разработчики Tile64 предусмотрели специальную технологию Multicore Hardwall для разбиения на разделы компьютеров на базе этих микросхем. Для этого одно или более ядер объединяются в «процессорный остров», коммуникации ядер которого с ядрами вне острова отсутствуют. При попытке пакета пересечь границу острова фиксируется прерывание, обрабатываемое программным обеспечением— гипервизором. Это позволяет работать с разными операционными системами на разных островах.

Для Tile64 обеспечена поддержка Linux 2.6. Кроме того, доступны средcтва разработки MDE (Multicore Development Environment), включающие интегрированную среду разработки на базе Eclipse, компилятор Си, графические средства отладки и профилирования и др. Для оптимизации программ можно применять коммуникационную библиотеку iLib, содержащую средства управления процессами, поддержки сокетов, а также обменов сообщениями и коммуникаций в модели общей оперативной памяти. Имеется также библиотека сетевого ввода/вывода NetI/O для балансировки нагрузки с распределением трафика между ядрами [11].

Приложения, на которые ориентировали Tile64 его разработчики, это в первую очередь встроенные сетевые приложения и обработка цифрового видео.

***

Применение современных высокопроизводительных процессоров предполагает усложнение работы программиста (как минимум— по распараллеливанию программы).

Специализированные ядра, подобные современным графическим процессорам Firestream 9170, целесообразно интегрировать в одну микросхему с ядрами общего назначения. Действительно, представим себе типовой современный узел HPC-кластера,— двухсокетовый сервер с четырехъядерными процессорами, содержащий всего восемь ядер. Распараллеленное приложение будет иметь восемь вычислительно-интенсивных нитей, каждая из которых хотела бы работать с собственным GPU для своего ускорения. Но если GPU будут на платах PCI-E x16, может просто не доставать нужных слотов, и не только задержки, но и пропускная способность каналов могут оказаться узким местом.

Подходы Intel и Tilera с интеграцией большого числа ядер и применением двухмерной решетки в качестве межсоединения могут оказаться весьма перспективными. При этом все ядра могут быть одинаковы (Tile64) или включать специализированные ядра, как это предполагает в качестве возможности Intel. n

Литература

-

S. Vangal, P. Kundu, Intelligent On-chip Interconnects: The 80-core Prototype and Beyond. Intel Development Forum, Spring 2007.

-

Tile Processor Architecture. Tilera Corp., Technology Brief, 2007.

-

J. Dongarra, Performance of various computers using standard linear equations software. Univ. Manchester Technical Report, Sept. 9th, 2007.

-

H. Q. Le, W. J. Starke e.a., IBM POWER6 microarchitecture. IBM J. Res. Dev., v. 51, №. 6, 2007.

-

T. Chen, R. Raghavan, J.N. Dale, Cell Broadband Engine Architecture and its first implementation— A performance View. IBM J. Res. Dev., v. 51, №. 5, 2007.

-

СlearSpeed Advance e620 Accelerator. СlearSpeed Technology, Product Brief, 2007.

-

Nvidia Tesla. GPU Computing Technical Brief, v.1.0.0, 2007.

-

B.G. Elmegreen, R.H. Koch e.a., Simulations of magnetic materials with MDGRAPE-2. IBM J. Res. Dev., v. 48, N. 2, 2004.

-

Б.Я.Цилькер, С.А.Орлов, «Организация ЭВМ и систем», Питер, М., 2004, 667 с.

-

W.J. Dally, P. Hanrahan e.a. Merrimac: Supercomputing with Streams. SC2003, Nov. 2003, Phoenix, Arizona.

-

M.B. Taylor, W.Lee e.a., Evaluation of the Raw Microprocessor: An Exposed-Wire Delay Architecture for ILP and Streams, 2004 ISCA.

Михаил Кузьминский— старший научный сотрудник ИОХ РАН (Москва). C ним можно связаться по тел. (499) 135-6388.

Голубой ген Голубого гиганта http://www.osp.ru/os/2006/10/3910032

Динозавры эпохи микропроцессоров http://www.osp.ru/os/2004/08/185070

Современные подходы к повышению производительности http://www.osp.ru/os/2006/05/2449839

Хочешь ядер самых разных? http://www.osp.ru/cw/2005/15/88619

Мультипроцессор Cell http://www.osp.ru/os/2006/05/2449872

На заре тера-эры http://www.osp.ru/cw/2007/06/3953436

Многоядерные процессоры AMD http://www.osp.ru/os/2005/10/380433