Проект International Technology Roadmap for Semiconductors (ITRS) объединяет усилия всех участников отрасли полупроводниковых устройств с тем, чтобы решить задачи, подразумеваемые в законе Мура. Представители международной рабочей группы International Technology Working Groups for Design and Test, поставив перед собой задачу сформулировать цели и направления исследования и разработки на ближайшие 15 лет, резюмировали мнение 839 экспертов из разных стран.

В последние 40 лет отрасль полупроводниковых устройств отличалась высокими темпами развития, которые были обусловлены способностью отрасли экспоненциально сокращать минимальный размер компонентов, используемых при производстве интегральных схем. Эту зависимость часто называют законом Мура.

International Technology Roadmap for Semiconductors (ITRS) стал одним из самых успешных международных совместных проектов, который позволяет сформулировать общее мнение специалистов отрасли о «наилучших текущих оценках» своих требований к исследованиям и разработке на ближайшие 15 лет. Roadmap является своего рода руководящим принципом для усилий компаний, исследовательских организаций и правительств, направленных на увеличение качества принимаемых на всех уровнях решений об инвестициях в исследования и разработку.

С момента начала проекта National Technology Roadmap for Semiconductors (NTRS) в 1992 году основная посылка всех материалов Roadmap состоит в том, что масштабирование (сокращение размеров компонентов) микроэлектроники будет продолжаться, что позволит на 25% сократить стоимость в расчете на функцию и поддерживать рост спроса на интегральные микросхемы на 15% ежегодно. В силу чего Roadmap составляется с учетом следующей задачи: какие технические возможности необходимо создать в отрасли, чтобы поддержать действие закона Мура?

Отрасль полупроводниковых устройств все больше и больше объединяет усилия в проведении исследований с помощью таких механизмов, как консорциумы и партнерские соглашения с поставщиками в среде, сохраняющей возможности для конкуренции. ITRS указывает основные технологические требования для координации таких совместных исследований. Это осуществляется двумя способами: за счет указания целей, которых должны достичь разрабатываемые сейчас технологические решения, и за счет определения областей, в которых не существует «известных решений», позволяющих с уверенностью продолжать масштабирование в некоторых аспектах полупроводниковой технологии. Поскольку последнее дает четкое представление о том, где исторический прогресс может подойти к концу, если в будущем в отрасли не удастся найти конкретные, фундаментальные решения, они определяют круг серьезных и увлекательных задач.

Существующие тенденции

Исторически сложилось так, что разработчики считают модули динамической оперативной памяти с произвольным доступом (dynamic random access memory — DRAM) стимулами к развитию технологии для всей отрасли полупроводниковых устройств. До начала 1990-х годов технология микросхем логики, примером которых могут служить микропроцессорные устройства (MPU), развивалась медленнее, чем технология DRAM. За последние несколько лет темпы разработки новых технологий, используемых при производстве микропроцессоров, выросли, и появление каждые четыре года нового поколения продуктов DRAM с плотностью вчетверо выше, чем у предыдущего поколения продуктов, теряет свою актуальность как способ определения технологических узловых точек. (Технологическая узловая точка отражает значительный прогресс в развитии технологии, определяемый размером самых мелких компонентов печатных схем — приблизительно на 70% меньше, чем в предыдущей узловой точке).

Масштабирование

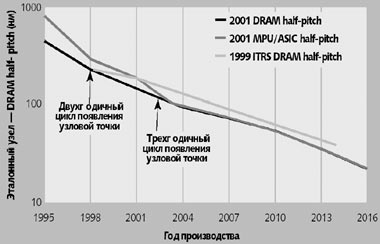

Микропроцессорные продукты ликвидируют исторически сложившийся технологический разрыв между ними и DRAM half-pitch, и теперь определяют развитие передовых инструментальных средств и процессов литографии, в частности в том, что качается «печати защитном слое» и физического размера вентиля. Как показано на рисунке 1 модули DRAM и микропроцессорные продукты делят роль лидера технологии, а кривая развития MPU half-pitch приближается к DRAM half-pitch. Фактически, MPU half-pitch «догонит» DRAM half-pitch в 2004 году; в предыдущей редакции ITRS предполагалось, что это слияние произойдет в 2015 году.

|

| Рис. 1. Сокращение сроков создания решений, прогнозируемых в ITRS Roadmap обусловлено тенденцией сближения характеристик MPU half-pitch и DRAM, и, как предполагается, их слияние будет достигнуто в 2004 году, а не в 2015, как прогнозировалось в 1999 Roadmap |

Несмотря на то что сокращение размеров компонентов происходит каждые три года примерно на 30%, размеры первых версий продуктов DRAM продолжают удваиваться каждые шесть лет, увеличиваясь на 12% в год. Это увеличение площади микросхемы обусловлено тем, что с каждым годом они должны содержать на 59% больше бит/конденсаторов/транзисторов в соответствии с формулировкой закона Мура, согласно которой количество функций на микросхему удваивается каждые 1,5 — 2 года. Однако чтобы поддержать исторически сложившуюся тенденцию сокращения соотношения затраты/функции на 25 — 30% в год, отрасль полупроводниковых устройств должна постоянно увеличивать производительность аппаратного обеспечения, наращивать объем производства, использовать подложки максимального размера и, самое важное, увеличивать число микросхем на подложке.

И модель DRAM, и модель MPU зависят от того, удастся ли добиться значительного усовершенствования процессов и архитектуры. Если этих целей достичь не удастся, производители будут вынуждены печатать микросхемы большего размера, чем предполагается в существующих документах Roadmap, или сократить темпы увеличения функциональности на микросхеме, указанные в законе Мура.

Тактовая частота

Помимо необходимости увеличивать функциональность, экспоненциально снижая затраты в расчете на функцию, имеется еще один фактор — спрос на более высокопроизводительные и недорогие продукты. Точно также, как согласно закону Мура, количество функций на микросхеме должно удваиваться каждые 1,5 — 2 года, чтобы удовлетворить спрос потребителей, существует соответствующее требование к увеличению скорости обработки электрических сигналов. В случае MPU число команд процессора в секунду также исторически удваивается каждые 1,5 — 2 года.

Что касается продуктов MPU, увеличение мощности процессоров, измеряемой в миллионах операций в секунду ((MIPs), достигается за счет сочетания исходной производительности технологии (тактовой частоты), умноженной на производительность архитектуры (число команд за такт процессора). Потребность во все более высокой операционной частоте, связанная с ростом размера микросхемы в среднем, будет по-прежнему стимулировать разработку новых процессов, архитектур и методов монтажа.

В таблице 1 учтены эти соображения. Самая высокая частота, достижимая в каждом из поколений продуктов, связана с производительностью самих транзисторов (на микросхеме, локальная тактовая частота) и эта связь становится даже более прямой по мере все более полного использования особенностей микроархитектуры (например, поддержки конвейеров).

Чтобы оптимизировать распространение сигнала и энергии по микросхеме, число уровней межсоединений, скорее всего, будет по-прежнему увеличиваться. По мере сокращения размеров межсоединений, в процессе производства микросхем будут все шире использоваться медные (с низким удельным сопротивлением) и различные внутриметаллические изоляционные материалы со значительно более низкой диэлектрической постоянной (k ~ 2-3). Проектировщики также будут применять методы мультиплексирования для увеличения операционной частоты между микросхемой и платой (вне платы).

В общем, распространение сигнала усложняется из-за увеличения емкостного и индуктивного связывания, которое снижает пиковые скорости и порождает временную неопределенность и потенциальные логические ошибки. Дополнительное затухание сигналов связано с индуктивностью пучков проводов и впаев при монтаже. Возможно, в конце концов, придется напрямую присоединять микросхемы для того, чтобы адекватным образом компенсировать вредные эффекты, вызванные монтажом.

Затраты

В таблице 1 также показаны тенденции изменения затрат. Способность ежегодно сокращать затраты в расчете на функцию на 25 — 30% — уникальная особенность отрасли полупроводниковых устройств, и является базовым механизмом, определяющим развитие. Чтобы обеспечить снижение затрат, необходимо постоянно увеличивать инвестиции в производство, а также в исследования и разработку. Даже на каждой фабрике в отдельности капитальные затраты на производство продолжают расти.

Однако 2001 Roadmap показывает, что размер транзисторов логики уменьшается только со скоростью совершенствования литографии (сокращение в 0,7 раза линейных размеров и в 0,5 раза площади в каждой из узловых технологических точек). Таким образом, чтобы сохранить неизменным размер микросхемы MPU, число транзисторов в каждой узловой технологической точке может только удваиваться. Поскольку темпы возникновения узловых технологических точек, как предполагается, после 2001 года вернуться к трехлетнему циклу, число транзисторов на микросхему MPU, начиная с 2001 года, может удваиваться только каждые три года. Усовершенствования в архитектуре битовых ячеек памяти DRAM также замедляется, и рост числа битов на микросхему в будущем также сократиться с тем, чтобы размер самих микросхем оставался приемлемым. Чтобы компенсировать уменьшение числа функций на микросхему в DRAM и MPU, придется предпринять более активные поиски альтернативных усовершенствований от эквивалентных преимуществ роста производительности микросхем, а также архитектур и структур системного уровня.

Даже несмотря на то, что темпы роста сложности микросхем в будущем могут снизиться, число функций на микросхеме по-прежнему будет расти. Возрастание числа функций на микросхеме приводит к увеличению сложности методов тестирования, что в прошлом выливалось в нелинейный рост затрат на создание тестов для дополнительного аппаратного обеспечения ATE (автоматизированное тестовое оборудование) и к увеличению времени тестирования устройств. Несмотря на то что согласно прогнозам затраты на ATE в расчете на пин снизятся, это более, чем компенсируется увеличением числа пинов в устройстве и ростом сложности. Встроенные решения для самотестирования (built-in self-test, BIST) и архитектуру, поддерживающую тестирование (design for testability, DFT) необходимо совершенствовать должны развиваться дальше, чтобы обеспечить критически важное снижение затрат на производственное тестирование, например, создание ATE с уменьшенным числом пинов.

Решение этих задач потребует усовершенствования во всех областях — особенно в новых интерфейсных процессах, которые преодолевают ограничения существующей технологии КМОП.

Проектирование системных драйверов

Предыдущие редакции ITRS неявно предполагали, что технологии должны развиваться линейным образом и, что новаторские решения будут использоваться во всех полупроводниковых продуктах. Сейчас применение новых технологических решений все больше и больше зависит от приложений. Оснащенные батарейками мобильные устройства заменяют серверы, подключенные к стационарной электрической сети, а архитектуры SoC и системы в пакетах, которые создаются их компонентов, получаемых из различных источников, вытесняют разработанные внутри одной компании единообразные архитектуры процессоров.

Документ 2001 ITRS обновляет и более точно определяет набор системных драйверов, которые использовались в предыдущих редакциях ITRS, предлагая количественные, внутренне согласованные модели, поддерживающие экстраполяцию и более гладко адаптирующиеся к будущим технологическим разработкам. Учитывая то, что природа DRAM хорошо понятна, ITRS сосредотачивается на массовых микропроцессорах, AMS и драйверах SoC.

Настраиваемые MPU

Настраиваемые MPU, выпускаемые в массовом порядке предполагают применение наиболее агрессивных стилей проектирования и производственных технологий. Именно для этих массовых компонентов разработчики вносят изменения в производственный цикл, создают новые стили проектирования и инструментальные средства поддержки (большие объемы прибыли могут быть направлены на создание новых инструментальных средств) и поднимают вопросы, касающиеся структуры миниатюрных микросхем. Таким образом, хотя разработка архитектур настраиваемых MPU требует больших трудозатрат, они позволяют создать новые технологии проектирования и производства и новые методы автоматизации, которые будут эффективно применяться во всей отрасли.

MPU — это часть сегмента, который стимулирует увеличение плотности интеграции и сложности архитектуры, соотношение энергоемкости и скорости работы, эффективности процесса проектирования в большой группе, тестирования и проверки, управления питанием и стоимости пакетных систем. Исторически сложилось так, что существовало два типа MPU, которые рассматривались в Roadmap: настольные системы среднего класса (cost-performance, CP) и высокопроизводительные (HP) серверы с постоянной площадью кристалла 140 квадратных миллиметров и 310 квадратных миллиметров соответственно.

Энергоемкость и стоимость — серьезные ограничители размера кристалла. Будущие MPU, скорее всего, потребуют создания объединенной настольно-серверной категории (сейчас различия между ними практически стерты) и мобильной категории (по существу, это низкоэнергоемкие, высокопроизводительные SoC).

Производительность проектирования, управление питанием, многоядерная организация, пропускная способность ввода/вывода, а также технология создания микросхем и процессов — вот основной контекст для будущей эволюции традиционного MPU.

Производительность проектирования. Сложность и стоимость проектирования и проверки продуктов MPU быстро растут и приближаются к тому уровню, где разработчикам приходится тысячи человеко-лет (и сформировать для этого группы проектировщиков из сотен специалистов) на создание одной архитектуры, и при этом процессоры, появляющиеся на рынке, изобилуют ошибками.

Управление питанием. Предельные уровни излучения энергии для приемлемого по цене монтажа, которые, по некоторым оценкам, к концу срока, на который распространяются прогнозы Roadmap, достигнут 50 Вт на квадратный сантиметр для воздушного охлаждения, невозможно сохранить так чтобы можно было поддерживать высокое напряжение. Исторически сложилось так, что это напряжение с каждым поколением изменяется в 0,85 раза вместо 0,7 раза, что требуется для идеального масштабирования, а частоты увеличиваются в 2 раза на поколение вместо идеальных 1,4.

Существовавшие ранее тенденции роста тактовой частоты системных драйверов MPU интерпретировались как требования к производительности для будущих устройств КМОП (скорость коммутации), приводящие к большим ветвлениям и очень тонким оксидам вентилей. Учитывая наличие таких устройств, MPU, в которых по-прежнему используются существующие методы создания микросхем и архитектур, к концу сроков, указанных в Roadmap, могут превысить ограничения на питание пакетов более, чем в 25 раз. С другой стороны, площадь, занимаемую логикой MPU, или деятельность логики необходимо будет уменьшить, чтобы удовлетворить ограничения пакета. Мобильные низкоэнергоемкие встроенные системы имеют более жесткие ограничения на питание, и подобные трудности могут возникнуть в этой области даже раньше, чем у MPU.

Эффективность питания для специализированного аппаратного обеспечения почти на четыре порядка больше, нежели для MPU общего назначения, и этот разрыв продолжает увеличиваться. В итоге, традиционные ядра обработки могут быть потеснены ориентированными на конкретные приложения или переконфигурируемыми механизмами обработки в будущих SoC-подобных MPU.

Многоядерная организация. В MPU с несколькими ядрами на кристалл сами ядра могут быть меньше и быстрее, чтобы противостоять глобальному масштабированию межсоединений, и разработчики могут оптимизировать их для повторного использования в различных приложениях и конфигурациях.

Кроме того, чтобы экономить энергию, многоядерные архитектуры могут использовать избыточность для увеличения объема производства. Будущая организация MPU, скорее всего, расширит иерархию памяти на плате, которая, пусть и относительно тривиальным образом, обеспечивает лучший контроль за утечкой и общим питанием микросхемы. Эволюционные изменения в микроархитектуре — суперконвейерные, суперскалярные методы прогнозирования — по-видимому, сходят на нет. Таким образом, для параллельной обработки будет расширена многопотоковая поддержка, а также возникнут более сложные аппаратные функции или специализированные механизмы для сетевых операций, графики, защиты и так далее. Компромиссы гибкость-эффективность постепенно заставят отказаться от систем обработки общего назначения.

Пропускная способность ввода/вывода. В системах MPU пины ввода/вывода, как правило, подключаются и к высокоуровневой кэш-памяти, и к основной системной памяти. Увеличение производительности процессоров требует увеличения пропускной способности ввода/вывода. Кэш-память уровня 2 и уровня 3 традиционно используют порт с самой высокой пропускной способностью, но в передовых архитектурах контроллер памяти интегрируется в кристалл процессора, чтобы сократить задержку при доступе к памяти. Эти прямые интерфейсы к памяти требуют большей пропускной способности ввода/вывода, чем интерфейс кэш-памяти.

Во многих архитектурах системная шина заменяется на высокоскоростные интерфейсы точка-точка, которые требуют более скоростной архитектуры ввода/вывода, поддерживая скорость свыше гигабита в секунду. Хотя последовательные каналы некоторое время назад достигли такой скорости, интеграция большого числа подобных устройство ввода/вывода на одном процессоре вызывает трудности при проектировании (каждая микросхема должна потреблять очень мало энергии), тестировании (тестерам необходимо быстро это запускать) и монтажа (пакеты должны действовать как сбалансированные линии передачи, в том числе соединения с микросхемой и платой).

Технология создания микросхем и процессов. Планы развития, касающиеся размеров компонентов и архитектуры устройств, подразумевают увеличение разнообразия процессов, в том числе создание более тонких и менее надежных оксидов вентилей, оптическая литография с нормой меньше длины волны, требующая серьезного улучшения средств нанесения разметки, и более высокая надежность при изменении процессов атомарного уровня, серьезно угрожает параметрическому объему выпуска (доллар на подложку после bin-sorting). Все это требует большего вмешательства на уровне проектирования архитектуры и микросхемы.

Хотя использование динамических микросхем оправдано с точки зрения производительности при более низкочастотных или clock-gated режимах, вопросы о запасе помехоустойчивости и уровне излучения энергии могут стать серьезными ограничениями при реализации такого подхода. Коррекция ошибок для однособытийного сбоя в логике будет расти по мере использования избыточности и переконфигурируемости для компенсации сокращения объема производства. Управление питанием потребует сочетания методов различных компонентных технологий. Оптимизация на уровне приложения операционной системы и архитектуры предполагает параллелизм, адаптивное напряжение и увеличение частоты. Новаторским решением станет более широкое использование методов, предусматривающих применение кремния на изоляторе.

Архитектуры аналоговых и смешанных сигналов

Архитектуры AMS включают в себя радиочастотные и аналоговые конвертеры, а также конвертеры, преобразующие аналоговые в цифровые и цифровые в аналоговые сигналы. Поскольку аналоговые процессоры предъявляют очень жесткие требования к архитектуре и технологии обработки, существенно отличающиеся от требований цифровых микросхем, масштабирование их в новые технологии — трудная задача. Хотя технологическое масштабирование всегда необходимо для цифровых микросхем, чтобы сократить энергопотребление, площадь и задержку, это не обязательно поможет в случае аналоговых микросхем, в которых поддерживать требования к точности или работать с сигналами из фиксированного диапазона напряжения намного труднее. В общем, микросхемы AMS (например, радиочастотные или встроенные пассивные) и технологии обработки (например, кремниево-германиевая) создают серьезные трудности при выполнении приемлемой по цене интеграции КМОП.

Требования точности также влияют на требования к инструментарию при проектировании аналоговых устройств. Проектирование цифровых микросхем следует набору правил, которые позволяют корректно функционировать вентилям логики. До тех пор, пока проектирование выполняется в соответствии с этими правилами, точного вычисления значений сигнала не нужно. Проектировщики аналоговых микросхем, с другой стороны, чтобы добиться требуемой точности должны учитывать некоторые эффекты второго порядка. Вдобавок, с этим связаны такие вопросы, как соединение (емкостных сопротивлений, индуктивности и подложки) и асимметрия (локальное изменение питания, а также имплантация, выравнивание, травление и другие производственные эффекты). Инструментальные средства анализа для этих задач, в основном, уже существуют, но для работы с ними нужны опытные пользователи; инструментальные средства синтеза, в лучшем случае, находятся на уровне предварительной разработки. Но задача производственного тестирования для микросхем AMS, по существу, неразрешима.

Для большинства современных архитектур, ориентированных на работу со смешанными сигналами, в частности, классических аналоговых архитектур, изменение напряжения представляет обработанный сигнал, а подаваемое напряжение определяет максимальный сигнал. Самыми сложными задачами в случае с устройствами для работы со смешанными сигналами, являются следующие.

- Снижение подаваемого напряжения, которое требует микросхем на токовых переключателях, зарядных устройств для увеличения напряжения и тщательной оптимизации уровней напряжения в микросхемах со стандартными ячейками.

- Увеличение относительных изменений параметров, что требует активных действий для компенсации несогласованности и компромиссов между скоростью и разрешением.

- Увеличение числа аналоговых транзисторов на микросхему, что требует более высокой скорости обработки и более качественной интеграции инструментальных средств моделирования смешанных сигналов.

- Увеличение скорости обработки (тактовых частот), что требует более точного моделирования устройств и межсоединений, а также возможности тестирования и интеграции на уровне системы и пакета.

- Увеличение утечки и помех, возникающих из-за интеграции SoC, что требует более точного моделирования помех и задержки и совершенно особого проектирования для радиочастотных микросхем.

- Недостаток навыков проектирования и снижение производительности, возникающих из-за отсутствия обучения и низкого уровня автоматизации, что требует обучения и базовых исследований в области средств проектирования.

Идеальный процесс проектирования предполагает повторное использование существующих архитектур для работы со смешанными сигналами и настройки параметров так, чтобы удовлетворить спецификациям на интерфейс между данным SoC и внешним миром. Однако такое повторное использование зависит от второго типа MOSFET (metal oxide semiconductor field-effect transistor), который не меняет свое максимальное операционное напряжение. Это приводит к спецификации Roadmap на КМОП-транзистор для работы со смешанными сигналами, который использует более высокое аналоговое подаваемое напряжение и не меняется в течение множества поколений цифровой технологии. Даже с таким устройством, однако, снижение напряжения и сокращение времени разработки аналоговых блоков микросхемы — главные препятствия на пути недорогого и эффективного масштабирования функций работы со смешанными сигналами.

Архитектура системы на плате

Развивающийся класс продуктов, архитектура SoC, объединяет в себе компоненты технологий различных классов системных драйверов, например, MPU, память, AMS и перепрограммируемые структуры, в широкий диапазон весьма сложных, массовых полупроводниковых продуктов. Как правило, технологии производства и проектирования SoC первоначально создавались для массовых настраиваемых драйверов. Учитывая, что основными целями являются снижение затрат на проектирование и более высокие уровни системной интеграции, класс драйверов SoC более всего похож на категорию ASIC.

Основное отличие между архитектурами ASIC и SoC состоит в том, что SoC особое значение придает повторному использованию интеллектуальной собственности (IP) для увеличения продуктивности. Кроме того, интеграция SoC потенциально охватывает гетерогенные технологии. SoC повторно используют и аналоговые, и массовые настраиваемые ядра, а также блоки программной технологии. Основное преимущество архитектур SoC состоит в том, что повторное использование блоков более эффективно и выгодно, чем использование эквивалентных архитектур, созданных «с нуля».

Вопрос о затратах служит стимулом для развертывания низкоэнергоемкого процесса и недорогих решений монтажа, параллельно с методологиями проектирования с быстрой оборачиваемостью (turnaround time, TAT). Последнее, в свою очередь, требует новых стандартов и методологий для описания IP, тестирования IP (в том числе, BIST и самовосстановление), синтеза интерфейсов блоков и так далее. Помимо необходимости совместной оптимизации микросхемы и пакета, вопрос об интеграции стимулирует спрос на гетерогенные технологии, такие как флэш, DRAM, MEMS, ферроэлектрическая RAM (FERAM), магниторезистивная RAM (MRAM) и химические датчики, которые реализуют компоненты конкретной системы. Таким образом, SoC — стимул для слияния множества технологий не только в одном и том же системном пакете, но и, потенциально, в одном и том же производственном процессе.

Поскольку архитектуры SoC предлагают недорогую и быструю реализацию системы, управление питанием и производительность при проектировании имеют важное значение для достижимого проектируемого пространства. 2001 ITRS определяет прототипное низкоэнергоемкое приложение SoC (LP-SoC) PDA и применяет два вида анализа для определения будущих требований к управлению питанием. Первый метод анализа принимает системные спецификации (0,1 Вт пиковая мощность и 2.1 мВт — мощность в резервном режиме) методом сверху вниз. Второй подход формирует требования к питанию снизу вверх, отталкиваясь от предполагаемого размера логики и памяти, а также параметров процесса и микросхемы. В таблице 1 показаны ограничения питания, прогнозируемые на период до 2016 года.

|

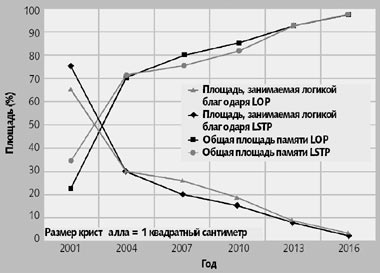

| Рис. 2. Влияние разрыва между уровнями энергопотребления на композицию микросхем. Размер модулей памяти превышает размер логики благодаря устройствам LSTP, поскольку у них более высокий уровень энергопотребления в рабочем режиме, чем у устройств LOP |

На рисунке 2 показаны прогнозы, касающиеся соединения логика/память для архитектур LP-SoC, предполагая, что питание микросхемы ограничено в соответствии с лимитом питания 0,1 Вт и что размер микросхемы не превышает 100 квадратных миллиметров. Размер памяти превышает размер логики в случае использования устройств LSTP (низкого энергопотребления в резервном режиме), поскольку они имеют значительно более высокую энергоемкость в рабочем режиме, чем устройства LOP (низкое энергопотребление в рабочем режиме). Без существенных улучшений возможностей управления питанием память будет асимптотически доминировать в обеих моделях к 2016 году. Учитывая прогноз, что размер микросхем PDA будет расти примерно на 20% в каждой узловой точке, несмотря на то, что уровень питания останется постоянным 0,1 Вт, в далекой перспективе это может привести к даже более существенному дисбалансу память-логика.

Проектирование

Важнейшее утверждение в 2001 Roadmap состоит в том, что стоимость проектирования — самая серьезная угроза сохранения феноменальных темпов развития отрасли полупроводниковых устройств. Производственные затраты на единовременный инжиниринг (nonrecurring engineering, NRE) составляют всего 1 млн. долл. (набор масок и тестовая плата), в то время как затраты NRE на проектирование регулярно достигают десятков миллионов долларов. Мы измеряем время производственного цикла в неделях, причем далеко не всегда, а время на проектирование и цикл проверки — месяцами и годами, причем с достаточной долей уверенности.

Несмотря на общепризнанную нехватку производительности при проектировании, при которой число имеющихся транзисторов растет быстрее, чем способность проектировать их содержательно, инвестиции в технологию процессов пока превосходят инвестиции в технологию проектирования. Тем не менее, разработчики продолжают добиваться прогресса в технологии проектирования (DT). По некоторым оценкам, затраты на проектирования низкоэнергоемких SoC PDA в 2001 году составили около 15 млн. долл., а не 342 млн. долл., если бы в области DT не были совершены открытия, сделанные с 1993 по 2001 год. Неприятный момент состоит в том, что теперь затраты на программное обеспечение, как правило, составляют около 80% затрат на разработку встроенных систем; затраты на тестирование растут относительно общей стоимости производства; инженеров, занимающихся проверкой, в группах, работающих над проектами, связанными с микропроцессорами, уже в два раза больше, чем инженеров, специализирующихся на проектировании, и этот список можно продолжать. В 2001 году многие недостатки технологии проектирования стали критическими.

Трудности, возникающие из-за сложностей

DT сталкивается с двумя основными видами сложностей: кремний и система. Сложности на уровне кремния связаны с влиянием масштабирования процесса и введением новых материалов или архитектур устройство/межсоединение. Ранее не принимаемое во внимание явление (косвенные трудности) теперь существенно влияют на корректность и ценность проектирования, и включают в себя следующие.

- Неидеальное масштабирование паразитных элементов устройств и потребляемое/пороговое напряжение - утечка, управление питанием, инновации на уровне микросхемы/устройства, подача питания.

- Связанные высокочастотные устройства и межсоединители - шум/помехи, анализ целостности сигнала и управление.

- Ограничения производственного оборудования - моделирование статистических процессов, описание библиотек.

- Масштабирование глобальной производительности межсоединений относительно производительности устройства - связь, синхронизация.

- Снижение надежности - туннелирование изоляторов вентиля и потеря целостности, джоулево тепло и перетекание электричества, однособытийный сбой, общая отказоустойчивость.

- Сложность автоматизации производства - совершенствование сетки и маскировка потока записи/контроля, затраты NRE.

- Многообразие процессов - описание библиотек, производительность аналоговых и цифровых микросхем, отказоустойчивая архитектура, повторное использование структур, надежные и предсказуемые платформы реализации.

Сложность на уровне кремния подвергает риску давно устоявшиеся парадигмы. Общесистемная синхронизация становится неосуществимой из-за ограничений питания и затрат на надежность при разнообразии производства; транзисторы КМОП становятся субъектом все более значительной статистической изменчивости в их поведении; производство микросхем со 100% работающими транзисторами и межсоединениями становится чрезмерно дорогим.

Сложность на уровне системы связана с экспоненциальным увеличением числа транзисторов, что стало возможно благодаря уменьшению их размеров и стимулируется спросом на большую функциональность, более низкие затраты и меньшем временем выхода на рынок. К таким трудностям относятся следующие.

- Повторное использование - поддержка иерархической архитектуры, гетерогенной интеграции SoC - моделирование, имитация, проверка и тестирование блоков компонентов - особенно AMS.

- Проверка и тестирование - получение спецификации, проектирование с учетом возможности получения контроля, проверка повторного использования для гетерогенных SoC, проверка на системном уровне и на уровне программного обеспечения, проверка AMS и новых устройств, доступ к тестам, самотестирование, интеллектуальное испытание на отказ шум/задержка, ограничение сроков для тестеров, повторное использование тестов.

- Оптимизация процесса проектирования, определяемая затратами - анализ и моделирование производственных затрат, параметры качества, совместная оптимизация на уровне кристалла-пакета-системы, оптимизация с учетом назначений различных систем, такими как отказоустойчивость и возможность проводить тестирование.

- Проектирование встроенного программного обеспечения - предсказуемые и базирующиеся на платформах методологии проектирования систем, совместное проектирование с аппаратными и предназначенными для сетевых систем средами, проверка/анализ программного обеспечения.

- Надежные в реализации платформы - предсказуемая реализация микросхем на различных фабриках по их производству, автоматизация более высокого уровня при реализации.

- Управление процессом проектирования - размер группы проектирования и ее географическая распределенность, управление данными, поддержка совместного проектирования, "система сквозного проектирования", управление цепочкой поставки, параметры, постоянное совершенствование процессов.

Все вместе сложности на уровне кремния и системы, как правило, приводят к суперэкспоненциальному увеличению сложности процесса проектирования. Чтобы бороться с этой сложностью, предлагается восемь всеобъемлющих методологических правил для будущей эволюции DT: применять повторное использование; быстро развивать DT; избегать итераций; заменять проверку на предупредительные меры; улучшать предсказуемость; разделять риски (например, за счет отделения поведения от архитектуры или вычисления от передачи данных); расширять сферу DT (вверх до уровня пакета и платы, вниз до уровня маски и процесса, от цифрового аппаратного обеспечения до программного обеспечения и AMS и так далее); унифицировать ранее разнородные области DT. Рисунок 3 показывает преобразование архитектуры системы проектирования в свете этих правил: традиционный каскад, в котором проектирование происходило независимо на различных уровнях, превращается в интегрированную систему, где логические, физические, монтажные и другие инструментальные средства могут работать вместе.

Вертикальные задачи

Roadmap определяет детальные задачи в соответствии с пятью традиционными областями DT: процесс проектирования; проектирование системного уровня; логика, микросхема и физическая архитектура; проверка проектирования; тестирование. Однако помимо перечисления этих детальных задач в 2001 Roadmap также указывается пять «вертикальных» задач, которые охватывают все взаимосвязи между автоматизацией проектирования электроники и другими отраслями, поддерживающими отрасль полупроводниковых устройств, чьи решения распределяются между всеми областями технологии проектирования. Мы всерьез рассчитываем на то, что задачи, которые невозможно решить в рамках одной технологический области ITRS, могут быть решены в рамках партнерства, связанного с технологией проектирования. Например, более быстрое распространение новых моделей наработки на отказ для помех и задержек пути, параллельно с соответствующими методами автоматической генерации тестовых шаблонов (automatic test pattern generation, ATPG) и BIST могут позволить преодолеть ограничения, связанные с тестовым оборудованием и скоростью.

Пять вертикальных задач — это производительность, питание, интеграция на производстве, помехи и устойчивость к ошибкам.

Производительность. Чтобы избежать экспоненциального роста затрат на проектирование, общая производительность спроектированных функций на микросхеме, а также производительность повторного использования (включая перенос) архитектуры, проверка и тестирование — в каждой узловой точке должны масштбироваться не более чем вдвое. Проверка превращается в узкое место, которое приобретает черты настоящего кризиса, требуя надежного и предсказуемого производства кремния, которое поддерживает автоматизацию системного проектирования более высокого уровня и, в частности, в области SoC, автоматизированные методы синтеза AMS, а также проверки и тестирования. Сокращение времени выпуска DT на рынок требует стандартов, которые позволят обеспечить стабильность, предсказуемость и интероперабельность.

Питание. Неидеальное масштабирование плоских устройств КМОП вместе с прогнозами Roadmap для материалов межсоединений и технологий монтажа, ставят множество задач, касающихся управления питанием и подачи электричества. Излучение электроэнергии MPU превысит пределы питания высокопроизводительных одномикросхемных пакетов в 25 раз к окончанию срока, на который распространяются прогнозы Roadmap, в то время как драйверы LP-SoC PDA требуют сохранения на постоянном уровне среднего энергопотребления и энергопотребления в резервном режиме даже по мере того, как размер логики и пропускная способность продолжают расти экспоненциально. DT должно решать вопросы, возникающие в связи с растущим разрывом в управлении питанием, при котором увеличение плотности питания ухудшает тепловое воздействие на надежность и производительность, а также уменьшение подаваемого напряжения ухудшает переключение электропитания и усиливает шум. Эти тенденции влияют на решения, касающиеся ресурсов межсвязывания на микросхеме, электропитания тестового оборудования и пределов динамического ответа, и даже существующих скрытых дефектов парадигм ускорения.

Производственная интеграция. Возможность возникновения будущих технологических узловых точек будет зависеть от совместного решения задач внутри отрасли как единого целого. Совместная оптимизация кристалла-пакета-платы и анализ могут увеличить стоимость реализации системы, проверку производительности и общего TAT проектирования, а также DT для системы в пакете. Новые DT для обеспечения корректности при вариативности производства, — например, проектировании микросхем с учетом возможных изменений, проектирование для поддержки правильности, оптимизация синхронизации и структуры, а также проверка статической производительности — могут смягчить требования контроля критических измерений при литографии, интеграции процессов, устройств и структур, интерфейсной обработки и в области технологии межсоединений. Наконец, более интеллектуальные интерфейсы, которые маскируют потоки производства и контроля, могут сократить производственные затраты NRE.

Помехи. Шум и помехи все сильнее мешают связи и синхронизации с эффективным использованием ресурсов, чьи глобальные тенденции масштабирования межсоединений уже подвергаются сомнению. Преобладающие методологии обеспечения целостности сигналов при проектировании логики, микросхем и физической архитектуры — хотя, по-видимому, масштабируются через узел в 100 нм — достигают своих пределов практичности. К этим методологиям относятся правила добавления повторителей для длинных межсоединений, правила контроля норм поворотов соединений и проектирование питания/распределения на поверхности для управления индуктивностью.

Масштабирование и интеграция SoC для компонентов, поддерживающих радиочастоты и смешанные сигналы, потребуют более гибких и мощных методологий. Среди возникающих вопросов — высота помещения шума (особенно в устройствах с низким энергопотреблением и в динамических микросхемах); большие показатели емкости и индуктивности связанных межсоединений; прерывание и отскакивание контактов IR для подачи напряжения; тепловое влияние на токоспускатели и сопротивления межсоединений на устройстве; формирование многослойной подложки. Основная задача DT — улучшить описание, моделирование, а также анализ и оценку шума и помех на всех уровнях проектирования.

Устойчивость к ошибкам. Устойчивость к ошибкам, корректировка и самовосстановление могут значительно увеличить объем производства, но потребуют дополнительных усилий на проверку и тестирование. Масштабирование технологий, скорее всего, стимулирует такую смену парадигмы, которая приведет к более внезапным и долговременным ошибкам в сигналах, значениях логики, устройствах и межсоединениях. Ниже 100 нм одномоментные сбои (мягкие ошибки) серьезно влияют на надежность продукта как на уровне памяти, так и на уровне логики. Атомарные эффекты масштабирования требуют новых «мягких» критериев дефектов, таких как некатастрофичное разрушение оксида вентиля.

В общем, автоматическое внедрение механизмов обеспечения надежности в архитектуру станет приоритетным по мере того, как система будет становиться слишком большой, чтобы выполнять для нее функциональное тестирование на выходе с производства. К возможным мерам относятся автоматическое представление избыточной логики и переконфигурируемости на микросхеме для поддержки отказоустойчивости, разработка адаптивных и самокорректирующихся или самовосстанавливающихся микросхем, и реализация отказоустойчивости на уровне программного обеспечения.

Тестирование

В течение многих лет функциональное тестирование на конвейере предоставляло надежную методологию для массового производства, позволяющую добиться требуемого уровня качества на выходе. Однако теперь складывается впечатление, что этот метод теряет свою актуальность по нескольким причинам, не последняя из которых — увеличение на уровне геометрической прогрессии инженерных ресурсов, необходимых для разработки тестов, и увеличение стоимости ATE. Сокращение объема производства, связанное с методологией функционального тестирования на конвейере, вызванного растущим разрывом между производительностью ATE и постоянно увеличивающимися скоростями ввода/вывода устройства, которые требуют повышенной точности для корректного разрешения сигналов синхронизации.

Хотя скорости полупроводников при передачи с микросхем увеличиваются на 30% в год, точность тестеров растет только на 12% в год. Предлагаемый тестерами типичный в 1980-х годах запас прочности в пять раз быстрее скорости устройства исчез. Если существующие тенденции сохраняться, ошибки тестеров при проверке синхронизации будут приближаться к времени цикла самых быстрых устройств. В 2001 году потери объема производства из-за неточности тестеров при использовании традиционной методологии тестирования во время производства уже практически превратились в серьезную проблему.

Более того, даже если модернизация или замена производственного тестового оборудования с каждым увеличением производительности устройства будет практически и финансово оправдана, избежать написания тестов вручную в функциональной тестовой среде, которая требует десятков человеко-лет для достаточно сложных архитектур — оказалось невозможно. Как следствие, поиск недорогих аппаратных решений, поддерживающих тестирование (design-for-test, DFT), до недавнего времени служил стимулом развития отрасли. Методики DFT, такие как сканирование и BIST, могут позволить автоматически генерировать содержимое тестов и, как минимум, значительно упростить задачу написания тестов вручную безотносительно к потенциальной экономии капитальных затрат. Устройства SoC с высоким уровнем интеграции требуют тщательно структурированного подхода DFT с тем, чтобы можно было повторно использовать тестовые результаты и избежать геометрического или экспоненциального роста усилий на разработку и проверку тестов и затрат на их производство.

Системы, поддерживающие тестирование

Активное сотрудничество между производителями полупроводниковых устройств и поставщиками тестового оборудования во время процесса формирования этих требований показало, что индивидуальные архитектуры с высоким уровнем настройки используют методологии DFT, которые сливаются в единый набор строительных блоков для тестеров. Это важное заключение создает уверенность в том, что разработчики ATE могут проектировать и конфигурировать общее оборудование DFT, которое соответствует требованиям отрасли, уменьшая потребность в настраиваемых решениях. Подход на базе DFT требует продолжения исследований, чтобы увеличить диапазон контролируемых дефектов процессов за счет разработки передовых методологий применения шаблонов на базе существующих моделей обработки ошибок к архитектурам и определения новых моделей обработки ошибок.

Даже в этом случае технология нанометровых процессов, увеличивающаяся скорость роста тактовой частоты, и интеграция SoC представляют серьезные задачи и могут ограничить применение традиционных методов DFT. Архитектуры SoC преодолевают традиционные барьеры между требованиями к тестовому оборудованию для цифровых, аналоговых, радиочастотных устройств, модулей памяти и устройствам работы со смешанными сигналами, что формирует тенденцию создания универсальных тестовых решений с широкими возможностями конфигурации. Рост спроса на пропускную способность на системном уровне и необходимость сохранить прежний или, даже уменьшить размер пакета, стимулируют широкое распространение новых высокоскоростных последовательных протоколов для внепроцессорных коммуникаций между устройствами разных типов. Аналоговая природа этих интерфейсов и необходимость поддерживать интероперабельность устройств порождают обширные требования к параметрическим тестам, выполняемым на конвейере, и к новым тестам и методам DFT в производстве.

Хотя методологии DFT в этих областях применимы, предполагается, что данная технология по-прежнему будет не в состоянии поддерживать производительность и сложность передовых устройств.

Высокоинтегрированные архитектуры SoC. Интеграция существующих архитектурных блоков в более крупные интегрированные устройства порождает нелинейный рост сложности инструментальных средств проектирования, DFT и производственных тестов, даже когда блоки являются гомогенными (например, вся логика). Все больше и больше устройства комбинируют аналоговые и смешанными сигналы и энергонезависимую флэш-память с логикой и RAM. Традиционные методы тестирования и оборудование ATE для этих типов устройств кардинально отличаются, в то время как сложность на уровне кремния и затраты для интегрированных устройств относительно предсказуемы. Таким образом, встроенные блоки и устройства смешанного типа порождают существенно нелинейный и непредсказуемый рост затрат на подготовку тестирования, проверку архитектуры и производственное тестирование.

Это оказывает влияние на процесс создания ASIC или макросов MPU, полностью встроенных в более крупные логические устройства, а затраты на производственное тестирование в некоторых случаях уже превышают стоимость кремния. Даже в случае DFT эти затраты могут быть нелинейными. Тестирование встроенных блоков прямого доступа DFT (direct-access DFT, DAT) может также привести к тому, что время тестирования вырастет на порядок по сравнению с временем тестирования невстроенных версий, в конченом итоге способствуя намного более широкому распространению BIST, чем представлялось ранее.

Более крупные части тестов потребуют расширения методов и протоколов DFT — например, IEEE P1500 — а также значительного использования BIST или базирующегося на программном обеспечении встроенного самотестирования для нейтрализации роста сложности тестирования, вызванного увеличением уровней интеграции архитектур.

Высокоскоростные интерфейсы устройств. Скорость компонента ввода/вывода становится столь же важной для системной производительности, как и тактовая частота ядра или производительность транзистора и архитектуры. Новые протоколы ввода/вывода действуют в многогигагерцовом диапазоне и являются намного более сложными — с синхронизацией источников, дифференциалом и даже с одновременно двунаправленными схемами, действующими на скорости несколько гигабит в секунду и с различным напряжением, которое изменяет часть диапазона поставляемого опорного напряжения (Vdd).

ATE и унаследованные методы тестирования компонентов включают в себя общее тестирование на базе тактовой частоты и параметров ввода/вывода в мегагерцовом диапазоне. Однако скорости и протоколы ввода/вывода порождают значительные инструментальные, материальные и ценовые задачи для оборудования ATE, аппаратного обеспечения интерфейсов и тестовых сокетов, необходимых как для проверки архитектуры, так и для производственного тестирования. Все это требует широкой отраслевой разработки и приложения возможностей тестирования на кристалле, особенно для ввода/вывода. Методы DFT и BIST для ввода/вывода, такие как кольцевая проверка, измерение колебаний и определение пиков станут стандартными методами для проверки и производственных тестов этих новых архитектур ввода/вывода. Без инноваций DFT понятно, что тенденция к высокоскоростному ввода/вывода на базе протоколов может привести ATE к тестовым решениям, ориентированным на конкретные протоколы, а это сложно и дорого.

Защита надежности. Исторически сложилось так, что при производственном тестировании не только измеряется производительность и функциональность устройств, но и выполняются необходимые бизнес-задачи по идентификации и выделению скрытых дефектов надежности или, более конкретно, недостатка надежности, порожденного дефектами. Экспоненциальное увеличение (примерно в десять раз в каждой узловой технологической точке) утечки электрического тока в передовых кремниевых технологиях накладывают серьезные ограничения на динамическое испытание на принудительный отказ, прямое истечение тока покоя IDDQ (direct drain quiescent current, IDDQ) и скачки напряжения выше Vdd во время тестирования.

Уменьшение отношения напряжения к номинальному Vdd ограничивает возможности ускорения, идентификации и защиты как при испытании на принудительный отказ, так и при колебании напряжения на ATE. На 180 нм и 130 нм тепловое излучение ограничивает использование температурных методик ускорения и порождает нелинейный рост затрат на принудительный отказ для продуктов старшего класса, таких как микропроцессоры. В то же время, с учетом существующих и прогнозируемых тенденций увеличения утечки электрического тока и фоновых токов, передовые методы IDDQ, такие как IDDQ delta, становятся весьма ограниченными из-за трудностей идентификации «сигнала» IDDQ в шуме фоновых токов.

В ближайшем будущем производственные затраты могут значительно возрасти как следствие увеличения объема производства (чрезмерного) и затрат на оборудование при расширении существующих подходов с целью сохранения темпов в соответствии с рыночными требованиями надежности.

Нужно ли функциональное тестирование?

По мере развития технологии затраты на оборудование для функционального тестирования уменьшаются для решений с фиксированными возможностями и остаются почти постоянными для решений с самой высокой производительностью.Однако предполагается, что DFT будет использоваться, когда необходимо ограничить диапазон производительности функционального тестирования в производстве за счет сокращения требований к скорости передачи данных при вводе/выводе, давая тем самым возможность выполнять тестирование небольшого числа пинов и позволяя в некоторых случаях отказаться от дорогих инструментов. DFT позволит производителям избавиться от утомительных технологических операций, связанных с оборудование функционального тестирования, и позволит увеличить уровень повторного использования этого оборудования для производственных тестов в разных технологических узловых точках.

В мире отладки и описания устройств функциональное и аналоговое тестирование во время работы будут выполняться по-прежнему и использоваться в качестве основного механизма определения основных причин ошибок и отклонений в процессах и архитектуре. В то же время, традиционные методологии на базе тестового оборудования будут необходимы для корреляции результатов, полученных на базе DFT. с условиями среды для конечного использования. Однако не предполагается, что это оборудование будет распространяться в производстве, а вместо этого оно будет применяться для проверки производственных возможностей на более дешевых массовых тестерах. Все это ставит серьезную задачу для отрасли.

Анализ отказов

Одна из наиболее важных задач ITRS Roadmap — добиться того, чтобы анализ отказов (FA) устройств и дефектов по-прежнему с успехом способствовал модернизации производства, что позволит создавать следующие поколения технологии. Перевод технологии КМОП на размер компонентов 65 нм ставит серьезную задачу для традиционного процесса FA по мере того, как характеристики и дефекты устройств (уже меньше оптической длины волны для микроскопических методик) становятся еще более скрытыми для даже передовых технологий физического FA.

Затраты и пропускная способность оборудования физического FA растут очень быстро, угрожая снизить предполагаемую скорости модернизации производства, которую предусматривает Roadmap. Чтобы сохранить темпы развития физический FA на базе аппаратного обеспечения, т. е. депроцессирование и физическое описание/контроль, останутся существенными, но станут во многом зависеть от программного обеспечения и методов диагностики на кристалле, применяемых для локализации ошибки. Увеличение чувствительности микросхемы требует поиска менее значительных и более стабильных дефектов. Сокращение нормы проектирования и меньшие размеры устройства требуют более высокого пространственного разрешения. Монтаж методом перевернутого кристалла и увеличение числа металлических слоев заставляют более активно применять методики фонового анализа, тем самым также увеличить пропускную способность так, чтобы получить актуальные результаты FA.

В силу совокупного воздействия этих факторов физический процесс FA станет слишком медленным и трудным, чтобы можно было рассчитывать на него как на обычную процедуру анализа. Необходимость в локализации ошибок на базе программного обеспечения, основная альтернатива/дополнение к традиционным методам локализации ошибок на базе аппаратного обеспечения, становится особенно острой, требуя кардинально новых решений.

Хотя мы не стремимся к тому, чтобы полностью описать здесь эти задачи, мы намерены дать читателям представление об обширных совместных усилиях, стоящих за этими потенциально новыми решениями и предложить им ознакомится с полным текстом отчета на Web-сайте ITRS (http://public.itrs.net/).

Благодарности

Мы выражаем признательность всем специалистам, приложившим усилия к тому, чтобы попытка, предпринятая в издании 2001 года материалов The International Technology Roadmap Semiconductors, увенчалась успехом.

Алан Аллан (alan.k.allan@intel.com) — инженер корпорации Intel. К области его научных интересов относятся технологии отрасли, а также моделирование и определение направлений развития экономики. Дон Эденфилд (donald.e.edenfeld@intel.com) отвечает за спецификации и выбор тестового оборудования в корпорации Intel. Эндрю Канг (abk@ucsd.edu) — профессор университета штата Калифорния (Сан-Диего). Уильям Джойнер (joyner@src.org) — научный сотрудник корпорации IBM. Майк Роджерс (michael.j.rodgers@intel.com) отвечает за интеграцию тестовых технологий в корпорации Intel. Йервант Зориан (zorian@logicvision.com) — вице-президент компании Virage Logic и старший советник по технологиям компании LogicVision.

Alan Allan, Don Edenfeld, William H. Joyner Jr., Andrew B. Kahng, Mike Rodgers, Yervant Zorian, 2001 Technology Roadmap for Semiconductors. IEEE Computer, January 2002. IEEE Computer Society, 2002. All rights reserved. Reprinted with permission.

Выдержки из Руководства (Executive Summary) и трех глав документа «Направления развития технологии на международном рынке полупроводниковых устройств» (The International Technology Roadmap for Semiconductors, 2001 edition, International Sematech, Austin, Texas, 2001).

Общее направление развития процессов и структур

Каждую главу ITRS, посвященную определенной технической области, готовит соответствующая международная рабочая группа International Technology Working Group (ITWG). Эти восемь ITWG соответствуют типичным видам деятельности, которые последовательно составляют цикл изготовления продукта: проектирование; тестирование; интеграция процессов, устройства и структуры; интерфейсные процессы; литография; межсоединения; интеграция производства; сборка и монтаж. Четыре дополнительных ITWG занимаются вертикальными решениями, которые, как правило, по отдельности перекрываются с циклом изготовления продукта в нескольких критически важных точках: окружающая среда, безопасность и здоровье; сокращение дефектов; измерения; моделирование и имитация.

Каждая ITWG получает информацию от Technology Working Groups (TWG) в пяти географических регионах: Европе, Японии, Корее, Тайване и США. Один — два делегата представляют каждую региональную TWG в соответствующей ITWG. Региональные TWG состоят из отраслевых экспертов, в том числе представляющих производителей микросхем, а также поставщиков оборудования и материалов, государственные исследовательские организации и университеты. В 2001 году всего 839 экспертов из пяти регионов на добровольной основе работали в 12 ITWG. В том числе, каждая TWG объединяла информацию, полученную от еще большего числа специалистов через конференции в рамках TWG и открытые семинары Roadmap.